## **Chapter 7 Basic Function Instruction**

|    |   | Т                    | 7- 2 |

|----|---|----------------------|------|

|    |   | С                    | 7- 5 |

|    |   | SET                  | 7- 8 |

|    |   | RST                  | 7-10 |

| 0  | : | MC                   | 7-12 |

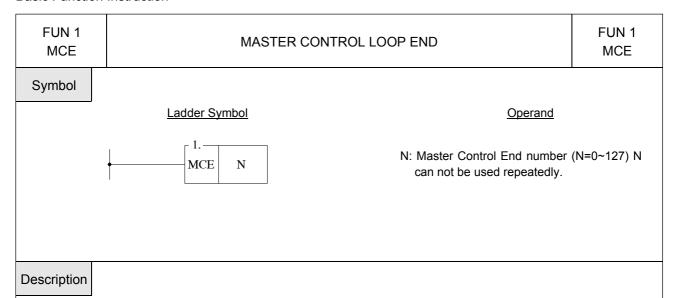

| 1  | : | MCE                  | 7-14 |

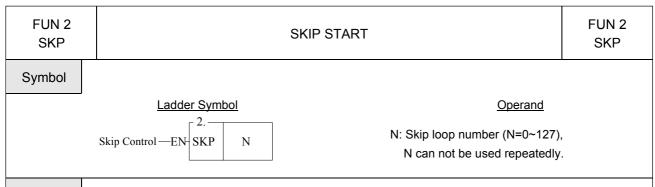

| 2  | : | SKP                  | 7-15 |

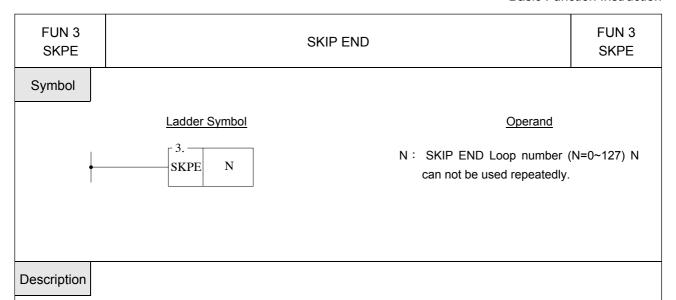

| 3  | : | SKPE                 | 7-17 |

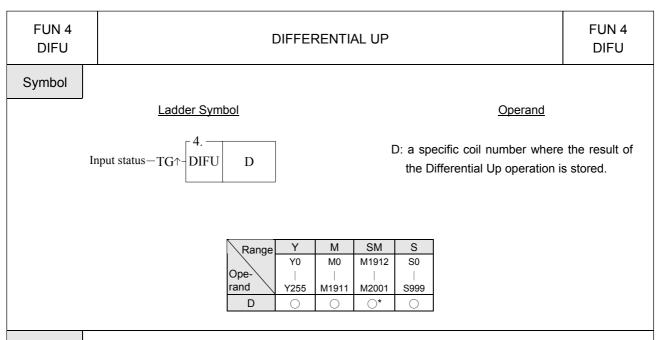

| 4  | : | DIFU                 | 7-18 |

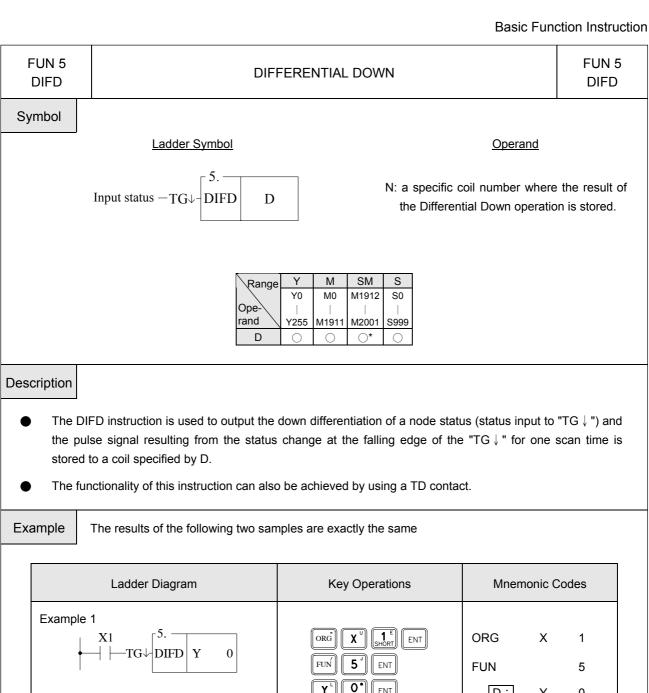

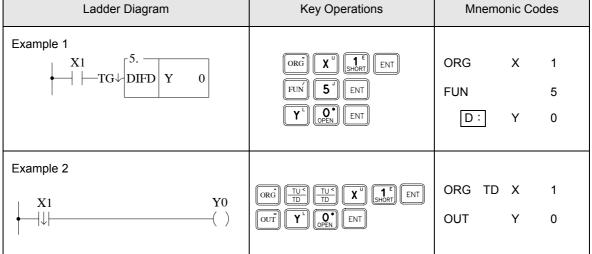

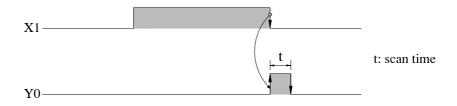

| 5  | : | DIFD                 | 7-19 |

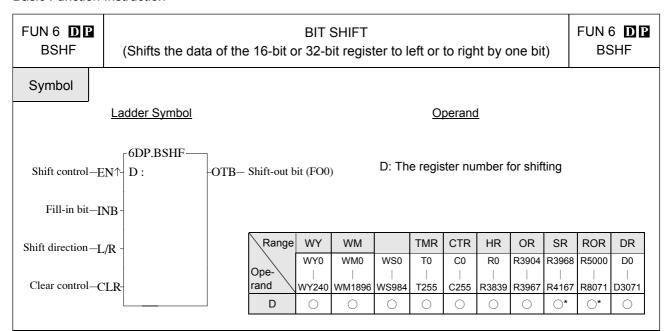

| 6  | : | BSHF                 | 7-20 |

| 7  | : | UDCTR                | 7-21 |

| 8  | : | MOV                  | 7-23 |

| 9  | : | MOV/                 | 7-24 |

| 10 | : | TOGG                 | 7-25 |

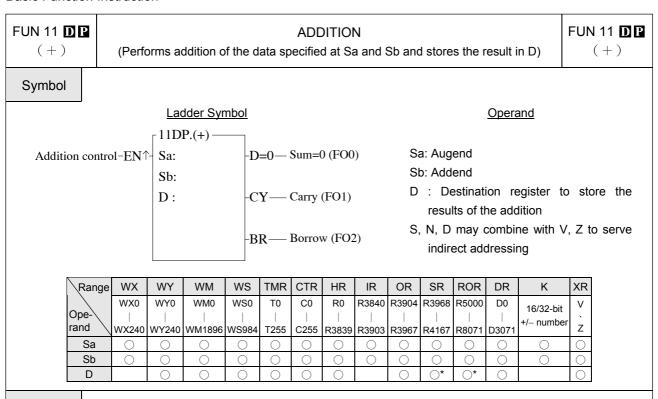

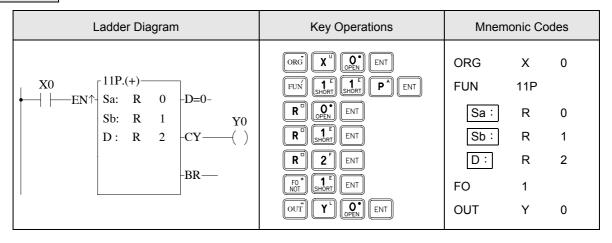

| 11 | : | (+)                  | 7-26 |

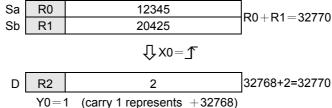

| 12 | : | (-)                  | 7-27 |

| 13 | : | (*)                  | 7-28 |

| 14 | : | (/)                  | 7-30 |

| 15 | : | <b>(</b> +1 <b>)</b> | 7-32 |

| 16 | : | (-1)                 | 7-33 |

| 17 | : | CMP                  | 7-34 |

| 18 | : | AND                  | 7-35 |

| 19 | : | OR                   | 7-36 |

| 20 | : | →BCD                 | 7-37 |

| 21 | : | $\rightarrow$ BIN    | 7-38 |

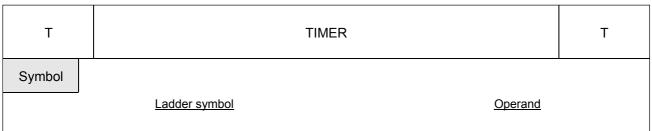

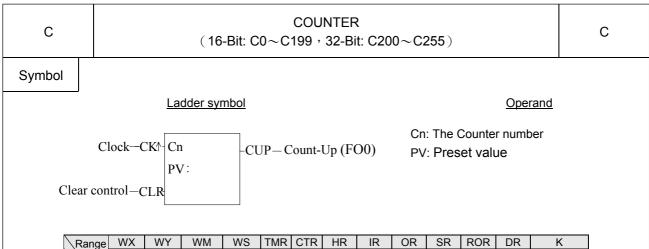

Tn: Timer Number.

PV: Preset value of the timer.

TB: Time Base (0.01S, 0.1S, 1S)

| Range  | WX      | WY      | WM         | WS      | TMR  | CTR  | HR    | IR    | OR    | SR    | ROR   | DR    | K     |

|--------|---------|---------|------------|---------|------|------|-------|-------|-------|-------|-------|-------|-------|

|        | WX0     | WY0     | WM0        | WS0     | T0   | C0   | R0    | R3840 | R3904 | R3968 | R5000 | D0    | 0     |

| Ope-   |         |         |            |         |      |      | 1     |       |       |       |       | - 1   |       |

|        | 140/0/0 | 140/0/0 | 14/8/4/000 | 14/0004 | TOFF | 0055 |       | D2002 | D2007 | D4407 | D0074 | D2074 | 00707 |

| rand \ | WX240   | WY240   | WM1896     | WS984   | T255 | C255 | R3839 | R3903 | R3967 | K4167 | R8071 | D3071 | 32/6/ |

| rand \ | WX240   | WY240   | WW1896     | WS984   | 1255 | C255 | R3839 | R3903 | R3967 | R4167 | R8071 | D3071 | 32/6/ |

● The total number of timers is 256 (T0~T255) with three different time bases, 0.01S, 0.1S and 1S.The default number and allocation of timers is shown as below (Can be adjusted according to user's actual requirements by the "Configuration" function):

T0 $\sim$ T49 : 0.01S timer (default as 0.00 $\sim$ 327.67S)  $\circ$  T50 $\sim$ T199 : 0.1S timer (default as 0.0 $\sim$ 3276.7S)  $\circ$  T200 $\sim$ T255 : 1S timer (default as 0 $\sim$ 32767S)  $\circ$

- FB-PLC programming tool will lookup the timer's time base automatically according to the "Memory Configuration" after the timer number is keyed in. Timer's time = Time base x Preset value. In the example 1 below, the time base T0 = 0.01S and the PV value = 1000, therefore the T0 timer's time = 0.01S x 1000 = 10.00S.

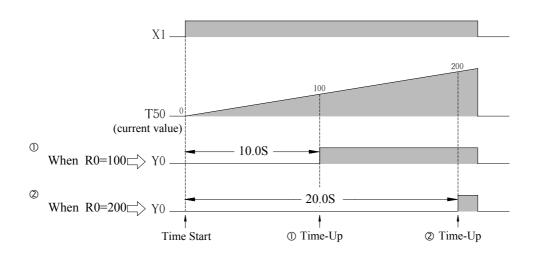

- If PV is a register, then Timer's time = Time base x register content. Therefore, you only need to change the register content to change the timer's time. Please refer to Example 2.

- \* The maximum error of a timer is a time base plus a scan time. In order to reduce the timing error in the application, please use the timer with a smaller time base.

#### Description

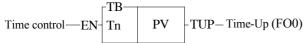

- When the time control "EN" is 1, the timer will start timing (the current value will accumulate from 0) until "Time Up" (i.e. CV≥PV), then the Tn contact and TUP (FO0) will change to 1. As long as the timer control "EN" input is kept as 1, even the CV of Tn has reached or exceeded the PV, the CV of the timer will continue accumulating (with M1957 = 0) until it reaches the maximum limit (32767). The Tn contact status and flag will remain as 1 when CV≥PV, unless the "EN" input is 0. When "EN" input is 0, the CV of Tn will be reset to 0 immediately and the Tn contact and "Time Up" flag TUP will also change to 0 (please refer to the diagram ① below).

- If the FBE/FBN-PLC OS version is higher than V3.0 (inclusive), the M1957 can be set to 1 so the CV will not accumulate further after "Time Up" and stops at the PV value. The default value of the M1957 is 0, therefore the status of M1957 can be set before executing any timer instruction in the program to individually set the timer CV to continue accumulating or stop at the PV after "Time Up" (please refer to the diagram ② below).

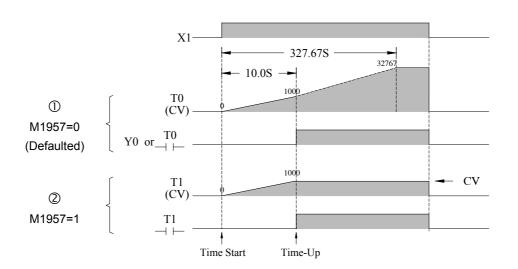

| Т         | TIMER                 | Т |

|-----------|-----------------------|---|

| Example 1 | Constant preset value |   |

| Ladder diagram                                           | Key operations                                | Mnemonic code                               |

|----------------------------------------------------------|-----------------------------------------------|---------------------------------------------|

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$    | ORG X LENT  T OPEN COPEN OPEN OPEN OPEN COPEN | ORG X 1<br>T0 PV: 1000                      |

| SET M1957  X1EN T1 1000 - TUP-                           | FO OPEN ENT OUT Y OPEN ENT                    | FO 0 OUT Y 0 ORG SHORT                      |

| An example of taking "Time-Up" signal directly from FO0. | ORG   1                                       | ORG SHORT  SET M 1957  ORG X 1  T1 PV: 1000 |

Example 2 Variable PV

The preset value (PV) shown in example 1 is a constant which is equal to 1000. This value is fixed and can not be changed once programmed. In many circumstances, the preset time of the timers needs to be varied while PLC running. In order to change the preset time of a timer, can first use a register as the PV operand (R or WX, WY...) and then the preset time can be varied by changing the register content. As shown in this example, if set R0 to 100, then T becomes a 10S Timer, and hence if set R0 to 200, then T becomes a 20S Timer.

| Т | TIMER | Т |  |

|---|-------|---|--|

|---|-------|---|--|

| Ladder diagram                                        | Key operations                                                                               | Mnemonic code                         |

|-------------------------------------------------------|----------------------------------------------------------------------------------------------|---------------------------------------|

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | ORG X U 1 ENT SHORT ENT  T' 5 OO HEX  PORG T' 5 OOEN ENT  ORG T' 5 OOEN ENT  OUT Y' OPEN ENT | ORG X 1 T 50 PV: R 0 ORG T 50 OUT Y 0 |

Remark: If the preset value of the timer is equal to 0, then the timer's contact status and FO0 (TUP) become 1 ("EN" input must be at 1) immediately after the PLC finishes its first scan because "Time-Up" has occurred. (TUP) stays at 1 until "EN" input changes to 0.

|    | \Range | WX      | WY       | WM          | WS                | TMR  | CTR  | HR     | IR     | OR     | SR    | ROR    | DR     | K          |

|----|--------|---------|----------|-------------|-------------------|------|------|--------|--------|--------|-------|--------|--------|------------|

|    |        | WX0     | WY0      | WM0         | WS0               | T0   | C0   | R0     | R3840  | R3904  | R3968 | R5000  | D0     | 0          |

| (  | Ope-\  |         |          |             |                   |      |      |        |        |        |       |        |        |            |

| ١, | rand \ | WYSAN   | W/>240   | WM1896      | MCOSA             | T255 | C255 | D3830  | D3003  | P3067  | R4167 | R8071  | D3071  | 2147483647 |

| Ι' | anu    | VV/\Z+U | VV 1 240 | VV IVI 1090 | W390 <del>4</del> | 1233 | 0233 | 173039 | 173903 | 113307 | 14101 | 110071 | D307 1 | 2147403047 |

| ľ  | Cn     | VVX240  | VV 1240  | VVIVI 1090  | W3904             | 1233 | 0233 | 13039  | 13903  | 113307 | 14107 | 110071 | D3071  | 2147403047 |

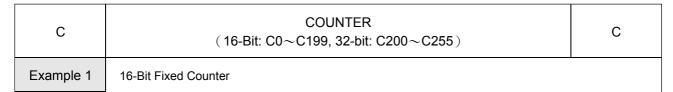

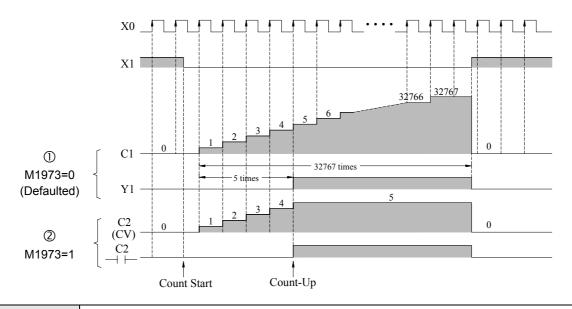

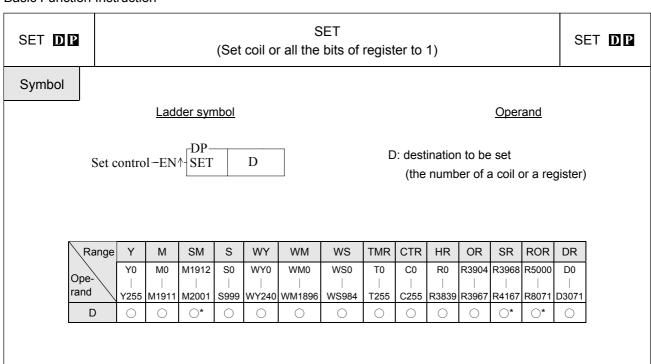

- There are total 200 16-Bit counters (C0~C199). The range of preset value is between 0~32767. C0~C139 are Retentive Counters and the CV value will be retained when the PLC turns on or RUN again after a power failure or a PLC STOP. For Non Retentive Counters, if a power failure or PLC STOP occurs, the CV value will be reset to 0 when the PLC turns on or RUN again.

- There are total 56 32-Bit counters (C200~C255). The range of the preset value is between 0~2147483647. C200~C239 are Retentive Counters and C240~C255 are Non Retentive Counters.

- The default number and assignment of the counters are shown below, if necessary can use the "CONFIGURATION" function to change the settings.

- To insure the proper counting, the sustain time of input status of CLK should greater than 1 scan time.

- The max. counting frequency with this instruction can only up to 20Hz, for higher frequency please use the high-speed soft/hardware counter.

#### Description

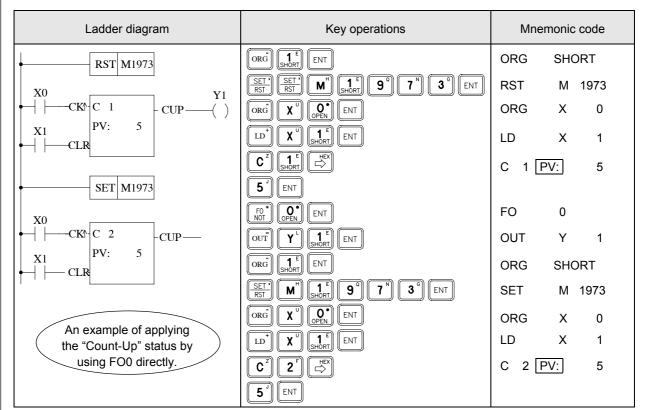

- When "CLR" is at 1, all of the contact Cn, FO0 (CUP), and CV value of the counter CV are cleared to 0 and the counter stops counting.

- When "CLR" is at 0, the counter is allowed to count up. The Counter counts up every time the clock "CK↑" changes from 0 to 1 (adds 1 to the CV) until the cumulative current value is equal to or greater than the preset value (CV>=PV), the counter "Count-Up" and the contact status of the counter Cn and FO0 (CUP) changes to 1. If the input status of clock continues to change, even the cumulative current value is equal and greater than the preset value, the CV value will still accumulate until it reaches the up limit at 32767 or 2147483647. The contact Cn and FO0 (CUP) stay at 1 as long as CV>=PV unless the "CLR" input is set to 1. (please refer the diagram ① below) ∘

- If the FBE/FBN-PLC OS version is higher than V3.0 (inclusive), the M1973 can set to 1 so the CV will not accumulate further after "Count Up" and stops at the PV. M1973 default value is 0, therefore the status of M1973 can be set before executing any counter instruction in the program to individually set the counter CV to continue accumulating or stops at the PV after "Count Up" (please refer to the diagram ② below).

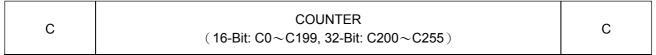

Example 2 32-Bit counter with variable preset value

Like a timer, if the PV of a counter is changed to a register (such as R, D, and so on), the counter will use the register contents as the counting PV. Therefore, only need to change the register contents to change the PV of the counter while PLC is running. Below is an example of a 32-bit counter that uses the data register R0 as the PV (in fact it is the 32-bit PV formed by R1 and R0).

| Ladder diagram                                                                                      | Key operations                                                                                              | Mner                    | monic                 | code                    |

|-----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-------------------------|-----------------------|-------------------------|

| X0 C200 PV: R 0 C200 Y1 C200 An example of applying the "time-up" status by using the C200 contact. | ORG X OOEN ENT  LD X LD SHORT ENT  C 2 2 OOEN OPEN COEN  R OOEN ENT  ORG C 2 FOOEN OPEN OPEN  OUT Y L 1 ENT | ORG LD C200 PV: ORG OUT | X<br>X<br>R<br>C<br>Y | 0<br>1<br>0<br>200<br>1 |

Remark: If the preset value of the counter is 0 and "CLR" input also at 0, then the Cn contact status and FO0 (CUP) becomes 1 immediately after the PLC finishes its first scan because the "Count-Up" has occurred. It will stay at 1 regardless how the CV value varies until "CLR" input changes to 1.

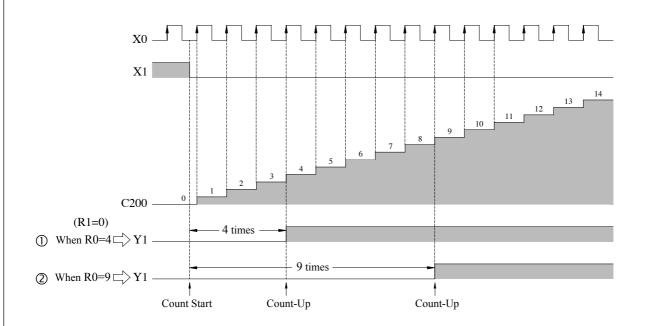

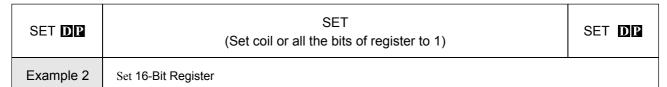

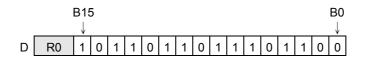

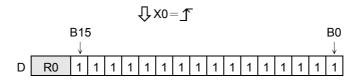

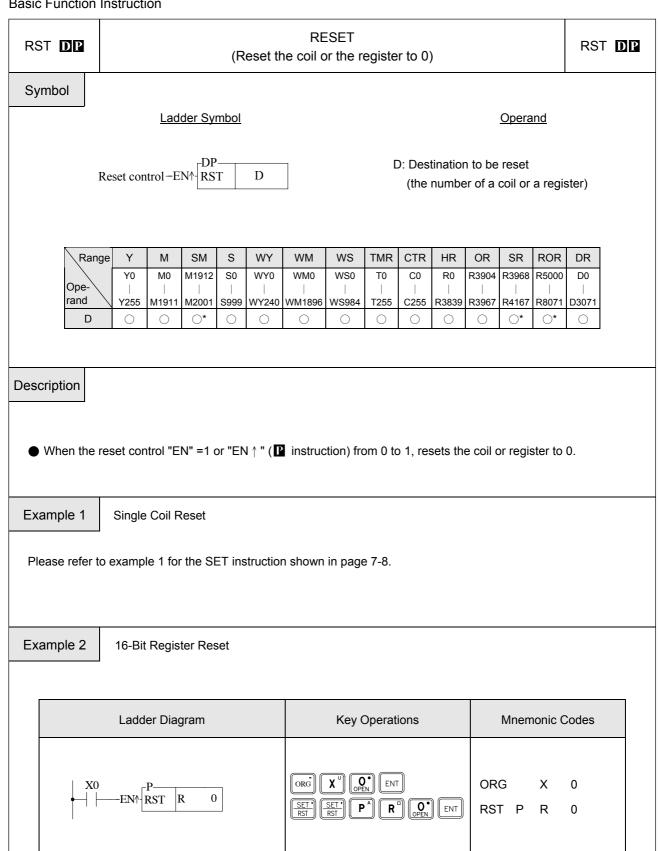

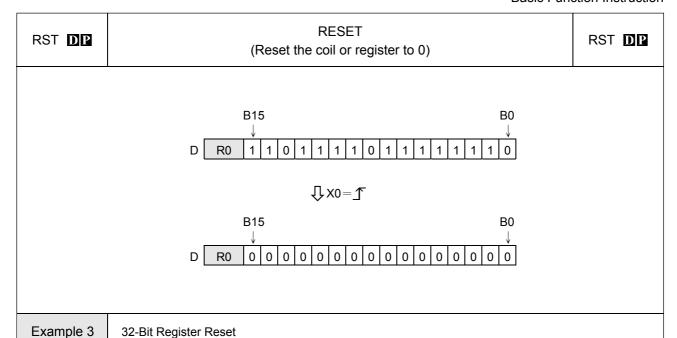

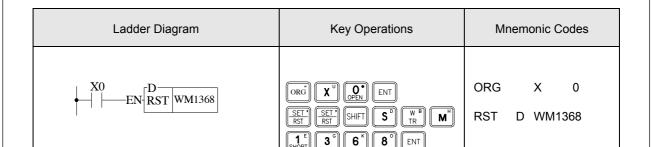

#### Description

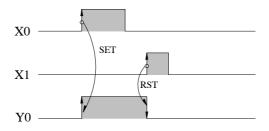

When the set control "EN" =1 or "EN↑" (☐ instruction) is from 0 to 1, sets the bit of a coil or all bits of a register to 1.

Example 1

Single Coil Set

| Ladder Diagram | Key Operations                             | Mr         | nemo | nic Co | odes |

|----------------|--------------------------------------------|------------|------|--------|------|

|                | ORG X OPEN ENT  SET P Y OPEN ENT  OPEN ENT | ORG<br>SET | Р    | X<br>Y | 0    |

|                | ORG X ENT                                  | ORG        |      | Х      | 1    |

|                | SET' SET' P' Y' OPEN ENT                   | RST        | Р    | Υ      | 0    |

|                |                                            |            |      |        |      |

| Ladder Diagram | Key Operations                            | Mnemonic Codes    |  |  |  |

|----------------|-------------------------------------------|-------------------|--|--|--|

| X0 P SET R 0   | ORG X U O ENT OPEN ENT  SET' P R OPEN ENT | ORG X 0 SET P R 0 |  |  |  |

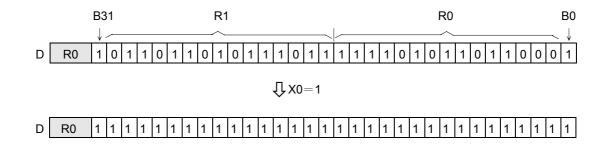

Example 3 32-Bit Register Set

| Ladder Diagram | Key Operations                             | Mnemonic Codes |        |   |  |

|----------------|--------------------------------------------|----------------|--------|---|--|

| X0 EN SET R 0  | ORG X" OFEN ENT  SET' SHIFT S" R" OFEN ENT | ORG<br>SET D   | X<br>R | 0 |  |

#### Description

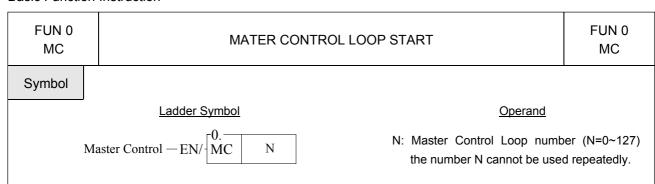

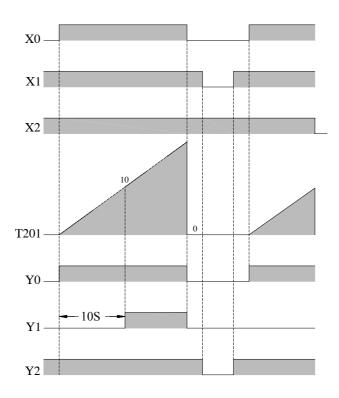

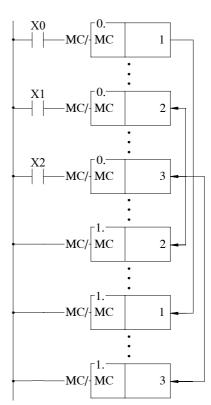

- There are a total of 128 MC loops (N=0~127). Every Master Control Start instruction, MC N, must correspond to a Master Control End instruction, MCE N, which has the same loop number as MC N. They must always be used in pairs and you should also make sure that the MCE N instruction is after the MC N instruction.

- When the Master Control input "EN/" is 1, then this MC N instruction will not be executed, as it does not exist.

- When the Master Control input "EN/" is 0, the master control loop is active, the area between the MC N and MCE N is called the Master Control active loop area. All the status of OUT coils or Timers within Master Control active loop area will be cleared to 0. Other instructions will not be executed.

#### Example

| Ladder Diagram |                            | Key Operations                                                                                                                                                                                                                                                                                                                                                                                      | Mnemo                                                  | nic Cod                   | les                                     |

|----------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|---------------------------|-----------------------------------------|

| X0             | Y0<br>—( )<br>—( )<br>—( ) | ORG X OPEN ENT  FUN OPEN ENT  SHORT ENT  ORG X 2 ENT  TY 2 OPEN HORT ENT  ORG T 2 OPEN SHORT ENT  OUT Y SHORT ENT  ORG T ENT  OUT Y SHORT ENT  ORG X SHORT ENT  OUT Y SHORT ENT  ORG X SHORT ENT | ORG FUN N: ORG OUT ORG T201 PV: ORG OUT FUN N: ORG OUT | X 0 1 X Y X ] T Y 1 1 X Y | 0<br>1<br>0<br>2<br>10<br>201<br>1<br>1 |

FUN 0 MC

#### MATER CONTROL LOOP START

FUN 0 MC

Remark1:MC/MCE instructions can be used in nesting or interleaving as shown to the right:

Remark2: • When M1918=0 and the master input changes from 0→1, and if pulse type function instructions exist in the master control loop, then these instructions will have a chance to be executed only once (when the first time the master control input changes from 0→1). Afterwards, no matter how many times the master control input changes from 0→1, the pulse type function instructions will not be executed again.

- When M1918=1 and the master control input changes from 0→1, and if pulse type function instructions exist in the master control loop, then each time the master control input changes from 0→1 the pulse type function instructions in the master control loop will be executed as long as the action conditions are satisfied.

- When a counting instruction exists in the master control loop, set M1918 to 0 can avoid counting error.

- When the pulse type function instructions in the master control loop must act upon the 0→1 input change by the master control, the flag M1918 should be set to 1.

- Every MCE N must correspond to a Master Control Start instruction. They must always be used as a pair and you should also make sure that the MCE N instruction is after the MC N instruction. After the MC N instruction has been executed, all output coil status and timers will be cleared to 0 and no other instructions will be executed. The program execution will resume until a MCE instruction which has the same N number as MC N instruction appears.

- MCE instruction does not require an input control because the instruction itself forms a network which other instructions can not connect to it. If the MC instruction has been executed then the master control operation will be completed when the execution of the program reaches the MCE instruction. If MC N instruction has never been executed then the MCE instruction will do nothing.

#### Description

Please refer to the example and explanations for MC instruction.

#### Description

- There are total 128 SKP loops (N=0~127). Every skip start instruction, SKP N, must correspond to a skip end instruction, SKPE N, which has the same loop number as SKP N. They must always be used as a pair and you should also make sure that the SKPE N instruction is after the SKP N instruction.

- When the skip control "EN" is 0, then the Skip Start instruction will not be executed.

- When the skip control "EN" is 1, the range between the SKP N and SKPE N which is so called the Skip active loop area will be skipped, that is all the instructions in this area will not be executed. Therefore the statuses of the discrete or registers in this Skip active loop area will be retained.

#### Example

|                                                       | Key Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Mnemonio                                                | Code                    | s                                  |

|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|-------------------------|------------------------------------|

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | () 2 ENT  () 2 ENT  () X U 1 ENT  () X U 2 ENT  () Y 2 OPEN HORT  () T 2 ENT  () T 2 | ORG FUN N: ORG OUT ORG T201 PV:  ORG OUT FUN N: ORG OUT | X 2 1 X Y X T Y 3 1 X Y | 0<br>1<br>0<br>2<br>10<br>201<br>1 |

| FUN 2<br>SKP | SKIP START                             | FUN 2<br>SKP |

|--------------|----------------------------------------|--------------|

|              | X0<br>X1<br>X2<br>Y1<br>Y2<br>Y1<br>Y2 |              |

- Every SKPE N must correspond to a SKP N instruction. They must always be used as a pair and you should also make sure that the SKPE N instruction is behind the SKP N instruction.

- SKPE instruction does not require an input control because the instruction itself forms a network which other instructions can not connect to it. If the SKP N instruction has been executed then the skip operation will be completed when the execution of the program reaches the SKPE N instruction. If SKP N instruction has never been executed then the SKPE instruction will do nothing.

#### Example

Please refer to the example and explanations for SKP N instruction.

**Remark**: SKP/SKPE instructions can be used by nesting or interleaving. The coding rules are the same as for the MC/MCE instructions. Please refer to the section of MC/MCE instructions.

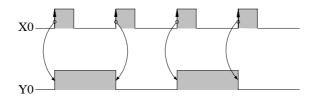

#### Description

- The DIFU instruction is used to output the up differentiation of a node status (status input to "TG  $\uparrow$ ") and the pulse signal resulting from the status change at the rising edge of the "TG  $\uparrow$ " for one scan time is stored to a coil specified by D.

- The functionality of this instruction can also be achieved by using a TU contact.

#### Example

The results of the following two samples are exactly the same

| Ladder Diagram                                                              | Key Operations                     | Mnemonic Codes       |

|-----------------------------------------------------------------------------|------------------------------------|----------------------|

| Example 1 $\begin{array}{c c} X1 & 4. \\ \hline & DIFU & Y & 0 \end{array}$ | ORG X 1 ENT  FUN 4 ENT  Y OPEN ENT | ORG X 1 FUN 4 D: Y 0 |

| Example 2                                                                   | ORG TU S SHORT ENT                 | ORG TU X 1 OUT Y 0   |

#### Description

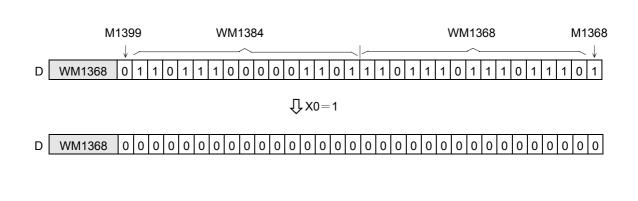

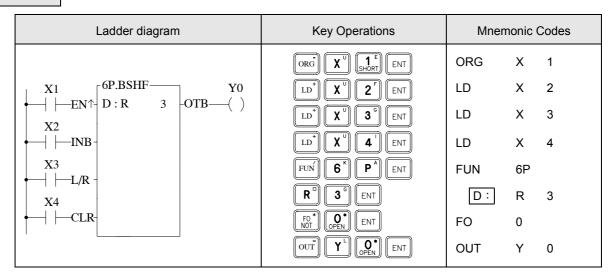

- When the status of clear control "CLR" is at 1, then the data of register D and FO0 will all be cleared to 0. Other input signals are all in effect.

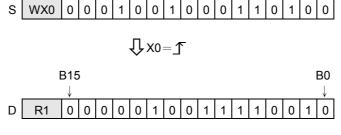

- When the status of clear control is "CLR" at 0, then the shift operation is permissible. When the shift control "EN" = 1 or "EN ↑" ( instruction) from 0 to 1, the data of the register will be shifted to right (L/R=0) or to left (L/R=1) by one bit. The shifted-out bit (MSB when shift to left and LSB when shift to right) for both cases will be sent to FO0. The vacated bit space (LSB when shift to left and MSB when shift to right) due to shift operation will be filled in by the input status of fill-in bit "INB".

#### Example

Shifts the 16-bit register data

FUN 7 D

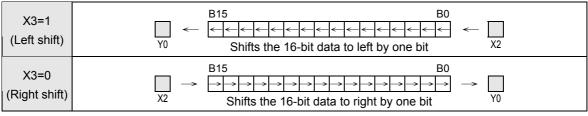

UDCTR

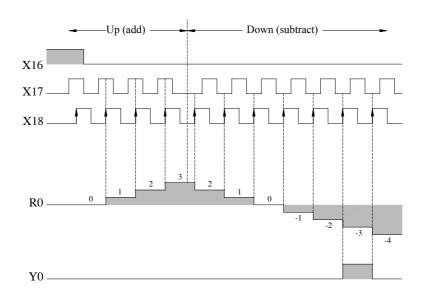

## UP/DOWN COUNTER (16-bit or 32-bit up and down 2-phase Counter)

FUN 7 D

UDCTR

#### Symbol

#### Ladder Symbol

#### Operand

CV: The number of the Up/Down Counter PV: Preset value of the counter or it's register number

| Range | WX                | WY                | WM                 | WS                | TMR             | CTR             | HR               | IR                  | OR                         | SR                  | ROR                 | DR               | K                       |

|-------|-------------------|-------------------|--------------------|-------------------|-----------------|-----------------|------------------|---------------------|----------------------------|---------------------|---------------------|------------------|-------------------------|

| Ope-  | WX0<br> <br>WX240 | WY0<br> <br>WY240 | WM0<br> <br>WM1896 | WS0<br> <br>WS984 | T0<br> <br>T255 | C0<br> <br>C255 | R0<br> <br>R3839 | R3840<br> <br>R3903 | R3904<br> <br> <br>  R3967 | R3968<br> <br>R4167 | R5000<br> <br>R8071 | D0<br> <br>D3071 | 16/32-bit<br>+/- number |

| CV    |                   | 0                 | 0                  | 0                 | 0               | 0               | 0                |                     | 0                          | O*                  | O*                  | 0                |                         |

| PV    | 0                 | 0                 | 0                  | 0                 | 0               | 0               | 0                | 0                   | 0                          | 0                   | 0                   | 0                | 0                       |

#### Description

- When the clear control "CLR" is 1, the counter's CV will be reset to 0 and the counter will not be able to count.

- When the clear control "CLR" is 0, counting will then be allowed. The nature of the instruction is a P instruction. Therefore, when the clock "CK↑" is 0→1 (rising edge), the CV will increased by 1 (if U/D=1) or decreased by 1 (if U/D=0).

- When CV=PV, FO0("Count-Up) will change to 1". If there are more clocks input, the counter will continue counting which cause CV≠PV. Then, FO0 will immediately change to 0. This means the "Count-Up" signal will only be equal to 1 if CV=PV, or else it will be equal to 0 (Care should be taken to this difference from the "Count-Up" signal of the general counter).

- The upper limit of up count value is 32767 (16-bit) or 2147483647 (32-bit). After the upper limit is reached, if another up count clock is received, the counting value will become −32768 or -2147483648 (the lower limit of down count).

- The lower limit of down count value is -32767 (16-bit) or -2147483647 (32-bit). After the lower limit is reached, if another down count clock is received, the counting value will become 32768 or 2147483648 (the upper limit of up count).

- If U/D is fixed as 1, the instruction will become a single-phase up count counter. If U/D is fixed as 0, the instruction will become a single-phase down count counter.

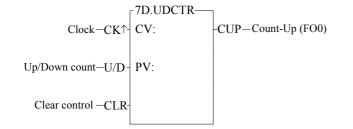

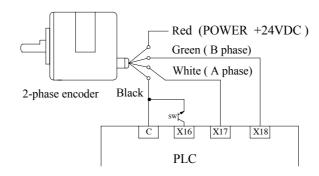

Example

The diagram below is an application example of UDCTR instruction being applied to an encoder.

| FUN | 7  | D |

|-----|----|---|

| UDO | СТ | R |

# UP/DOWN COUNTER (16-bit or 32-bit up/down 2-phase Counter)

FUN 7 D

UDCTR

| Ladder Diagram                                        | Key Operations                                                                                                            | Mnemonic Codes               |                                 |                          |

|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|------------------------------|---------------------------------|--------------------------|

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | ORG X U 1 B O ENT  LD X U 1 F 7 ENT  LD X U 1 F 6 ENT  FUN 7 ENT  R O O ENT  SHIFT OR 3 ENT  FO' OPEN ENT  OUT Y OPEN ENT | ORG LD LD FUN CV: PV: FO OUT | X<br>X<br>7<br>R<br>-<br>0<br>Y | 18<br>17<br>16<br>0<br>3 |

**Remark 1**: Since the counting operation of UDCTR is implemented by software scanning, therefore if the clock speed is faster than the scan speed, lose count may then happen (generally the clock should not exceed 20Hz depending on the size of the program). Please use the software or hardware high-speed counter in the PLC. Refer to the "High Speed Counter Application" in the Advanced Manual.

**Remark 2**: In order to ensure the proper counting, the sustain time of the status of clock input should greater than 1 scan time.

+/- numbe

$\bigcirc$

Ζ

0

Ope-

rand

S

D

WX240

WY240

$\bigcirc$

WM1896

$\bigcirc$

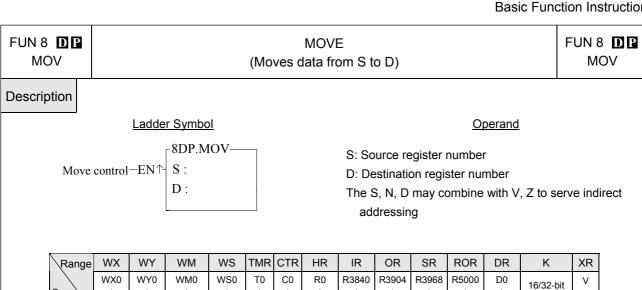

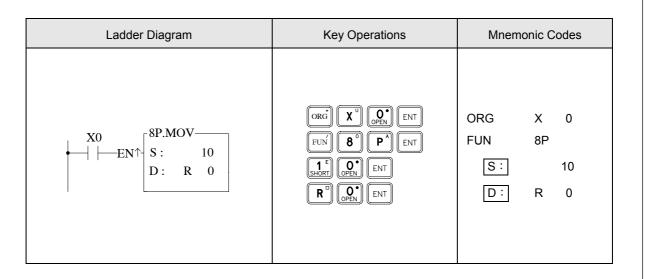

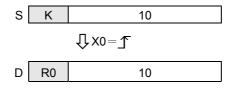

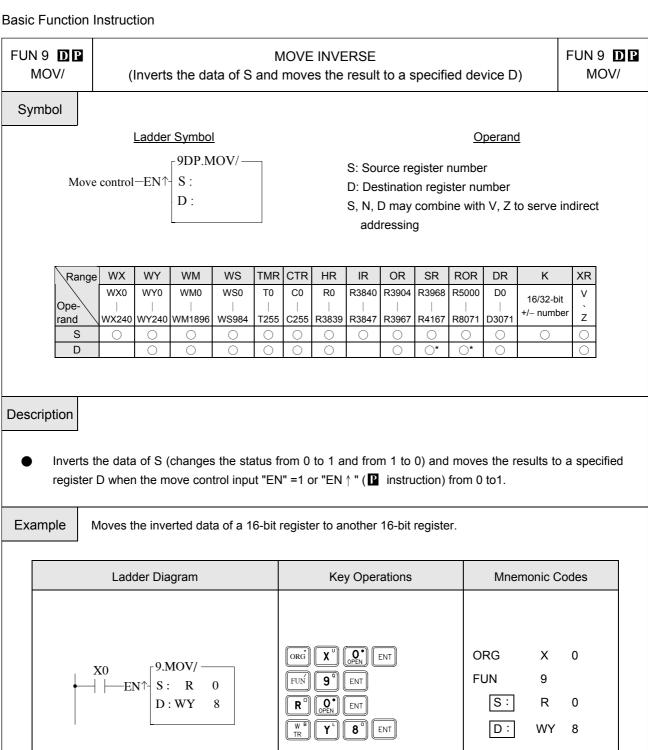

Moves (writes) the data of S to a specified register D when the move control input "EN" =1 or "EN↑" ( ■ instruction) from 0 to 1.

R3839

$\bigcirc$

R3903

$\bigcirc$

R3967

R4167

R8071

$\bigcirc$

D3071

#### Example

Description

Writes a constant data into a 16-bit register.

WS984

C255

T255

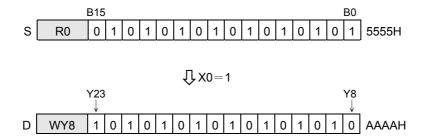

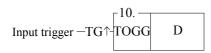

FUN 10 TOGGLE SWITCH FUN 10

TOGG (Changes the output status when the rising edge of control input occur) TOGG

#### Symbol

#### Ladder Symbol

#### Operand

D: the coil number of the toggle switch

| Range | Υ    | М     | SM        | S    |

|-------|------|-------|-----------|------|

|       | Y0   | MO    | M1912     | S0   |

| Ope-  |      |       |           |      |

| rand  | Y255 | M1911 | M2001     | S999 |

| D     | 0    | 0     | <b>O*</b> | 0    |

#### Description

The coil D changes its status (from 1 to 0 and from 0 to 1) each time the input "TG↑" is triggered from 0 to 1 (rising edge).

#### Example

| Ladder Diagram                                                   | Key Operations                                 | Mnemonic Codes        |  |  |  |

|------------------------------------------------------------------|------------------------------------------------|-----------------------|--|--|--|

| $ \begin{array}{c c} X0 & 10. \\ \hline TOGG Y & 0 \end{array} $ | ORG X U OPEN ENT  FUN 1 E OPEN ENT  Y OPEN ENT | ORG X 0 FUN 10 D: Y 0 |  |  |  |

#### Description

Performs the addition of the data specified at Sa and Sb and writes the results to a specified register D when the add control input "EN" =1 or "EN ↑" ( instruction) from 0 to 1. If the result of addition is equal to 0 then set FO0 to 1. If carry occurs (the result exceeds 32767 or 2147483647) then set FO1 to 1. If borrow occurs (adding negative numbers resulting in a sum less than -32768 or -2147483648), then set the FO2 to 1. All the FO statuses are retained until this instruction is executed again and overwritten by a new result.

## Example 16-bit addition

#### Description

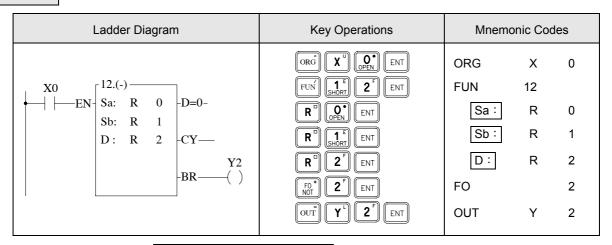

Performs the subtraction of the data specified at Sa and Sb and writes the results to a specified register D when the subtract control input "EN" =1 or "EN↑" ( instruction) from 0 to 1. If the result of subtraction is equal to 0 then set FO0 to 1. If carry occurs (subtracting a negative number from a positive number and the result exceeds 32767 or 2147483647), then set FO1 to 1. If borrow occurs (subtracting a positive number from a negative number and the resulted difference is less than -32768 or -2147483648), then set FO2 to 1. All the FO statuses are retained until this instruction is executed again and overwritten by a new result.

#### Example

16-bit subtraction

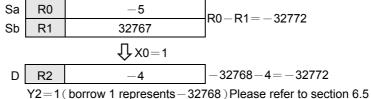

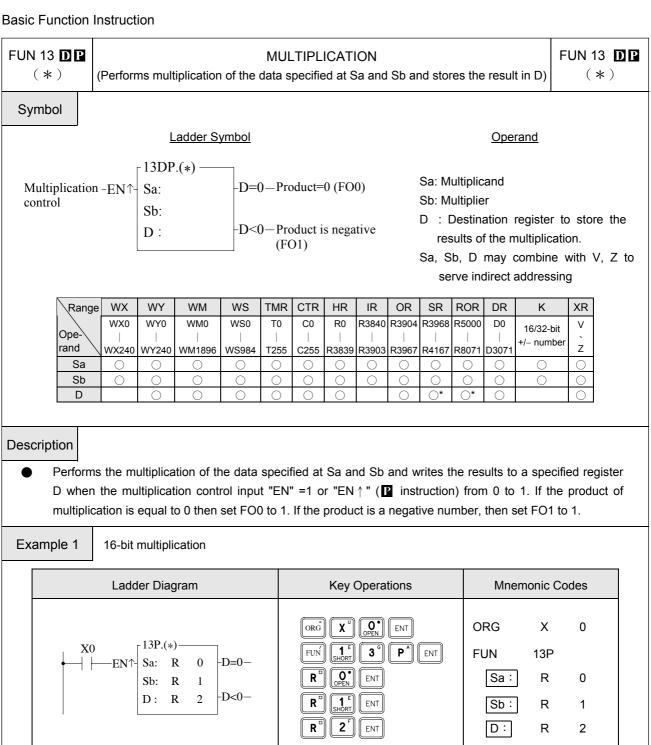

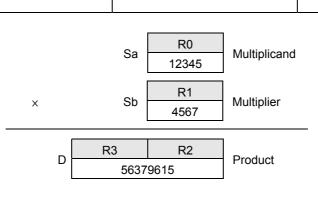

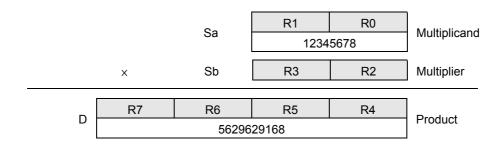

| FUN 13 <b>DP</b> (*) | MULTIPLICATION (Performs multiplication of the data specified at Sa and Sb and stores the result in D) | FUN 13 <b>DP</b> (*) |

|----------------------|--------------------------------------------------------------------------------------------------------|----------------------|

| Example 2            | 32-bit multiplication                                                                                  |                      |

| Ladder Diagram                     | Key Operations                                                        | Mnemonic Codes                          |  |  |  |

|------------------------------------|-----------------------------------------------------------------------|-----------------------------------------|--|--|--|

| X0<br>Sa: R 0<br>Sb: R 2<br>D: R 4 | ORG X OPEN ENT  FUN 1 3 SHIFT S ENT  R D OPEN ENT  R 2 ENT  R D 4 ENT | ORG X 0 FUN 13D  Sa: R 0 Sb: R 2 D: R 4 |  |  |  |

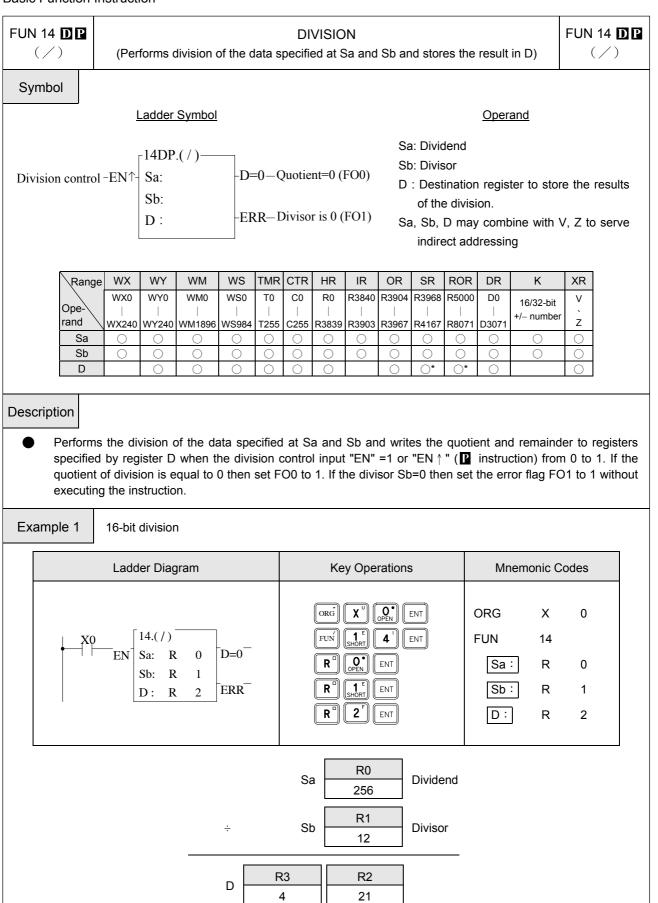

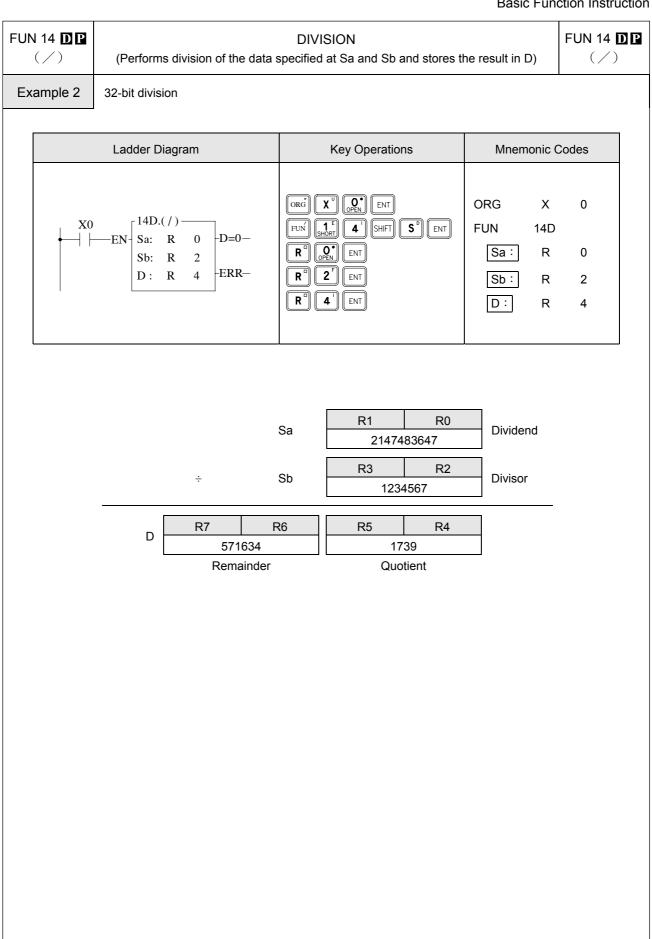

Quotient

Remainder

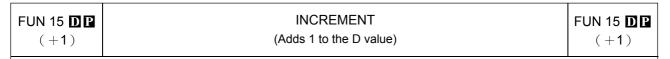

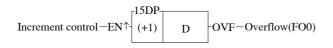

#### Ladder symbol

#### Operand

D : The register to be increased

D may combine with V, Z to serve indirect

addressing

| Range | WY    | WM     | WS    | TMR  | CTR  | HR    | OR    | HR    | HSCR  | RTCR  | SR        | ROR       | DR      |

|-------|-------|--------|-------|------|------|-------|-------|-------|-------|-------|-----------|-----------|---------|

| _ \   | WY0   | WM0    | WS0   | T0   | C0   | R0    | R3904 | R3920 | R4096 | R4128 | R4136     | R5000     | D0      |

| Ope-  |       |        |       |      |      |       |       |       |       |       |           |           |         |

| rand  | WY240 | WM1896 | WS984 | T255 | C255 | R3839 | R3919 | R4047 | R4127 | R4135 | R4167     | R8071     | D3071   |

| D     | 0     | 0      | 0     | 0    | 0    | 0     | 0     | 0     | 0     | 0     | <b>O*</b> | <b>O*</b> | $\circ$ |

Adds 1 to the register D when the increment control input "EN" =1 or "EN↑" ( instruction) from 0 to 1. If the value of D is already at the upper limit of positive number 32767 or 2147483647, adding one to this value will change it to the lower limit of negative number -32768 or -2147483648. At the same time, the overflow flag FO0 (OVF) is set to 1.

Example

16-bit increment register

| Ladder diagram                                                                              | Key operations                                        | Mnemonic code             |

|---------------------------------------------------------------------------------------------|-------------------------------------------------------|---------------------------|

| $ \begin{array}{c c} X0 \\ \hline  \uparrow  - EN \\ \hline (+1) R 0V - OVF - \end{array} $ | ORG TUS X OPEN ENT  FUN 1 E 5 ENT  R OPEN SHIFT T ENT | ORG TU X 0 FUN 15 D: R 0V |

When

$$V = 100 \cdot 0 + 100 = 100$$

D R100 1

$V = V = V = 100$

R100 2

FUN 16 **D P DECREMENT** FUN 16 **DP** (-1)(Subtracts 1 from the D value) (-1)Ladder symbol Operand -16DP D : The register to be decreased Decrement control -EN^-(-1) -UDF-Underflow(FO0) D D may combine with V, Z to serve indirect addressing WY WM WS **TMR** CTR HR OR HR **HSCR** RTCR SR ROR DR Range WY0 WM0 WS0 T0 C0 R0 R3904 R3920 R4096 R4128 R5000 D0 R4136 Ope rand WY240 WM1896 WS984 T255 C255 R3839 R3919 R4047 R4127 R4135 R4167 R8071 D3071 Description Subtracts 1 from the register D when the decrement control input "EN" =1 or "EN↑" ( instruction) from 0 to 1. If the value of D is already at the lower limit of negative number -32768 or -2147483648, subtracting one from this value will change it to the upper limit of positive number 32767 or 2147483647. At the same time, the underflow flag FO0 (UDF) is set to 1. Example 16-bit decrement register Mnemonic code Ladder diagram Key operations ORG Χ 0 <sub>↑</sub> 16P. **P** \* | | ENT FUN 16P 0 UDF D : R 0 D R0 0  $\int X0 = \int$ R0

####

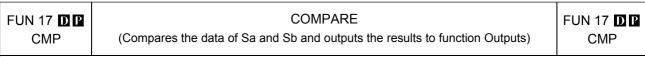

| Range     | WX        | WY        | WM         | WS        | TMR      | CTR  | HR    | IR    | OR    | HR    | HSCR        | RTCR      | SR        | ROR   | DR    | K         |

|-----------|-----------|-----------|------------|-----------|----------|------|-------|-------|-------|-------|-------------|-----------|-----------|-------|-------|-----------|

| 07.5      | WX0       | WY0       | WM0        | WS0       | T0       | C0   | R0    | R3804 | R3904 | R3920 | R4096       | R4128     | R4136     | R5000 | D0    | 16/32 bit |

| Ope-\rand | <br>WX240 | <br>WY240 | <br>WM1896 | <br>WS984 | <br>T255 | C255 | R3839 | R3903 | R3919 | R4047 | <br>  R4127 | <br>R4135 | <br>R4167 | R8071 | D3071 | +/-number |

| Sa        | 0         | 0         | 0          | 0         | 0        | 0    | 0     | 0     | 0     | 0     | 0           | 0         | 0         | 0     | 0     | 0         |

| Sb        | 0         | 0         | 0          | 0         | 0        | 0    | 0     | 0     | 0     | 0     | 0           | 0         | 0         | 0     | 0     | 0         |

Compares the data of Sa and Sb when the compare control input "EN" =1 or "EN↑" (P instruction) from 0 to 1. If the data of Sa is equal to Sb, then set FO0 to 1. If the data of Sa>Sb, then set FO1 to 1. If the data of Sa<Sb, then set FO2 to 1. If the data of Sa < Sb, then set the FO2 to 1.</p>

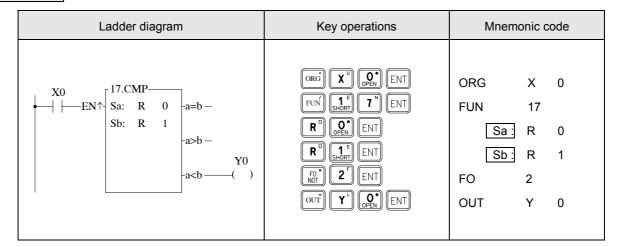

#### Example Compares the data of 16-bit register

- From the above example, we first assume the data of R0 is 1 and R1 is 2, and then compare the data by executing the CMP instruction. The F00 and F01 are set to 0 and F02 (a<b) is set to 1 since a<b.

- If you want to have the compound results, such as  $\ge \cdot \le \cdot < >$  etc., please send =  $\cdot <$  and > results to relay first and then combine the result from the relays.

- M1919=0, when this command in not executed, FO0, FO1, FO2 will remain in the status at last execution.

- M1919=1, when this command in not executed, FO0, FO1, FO2 are all cleared to 0.

- Control M1919 properly to obtain memory-holding function for functional command output.

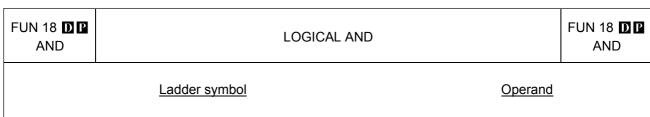

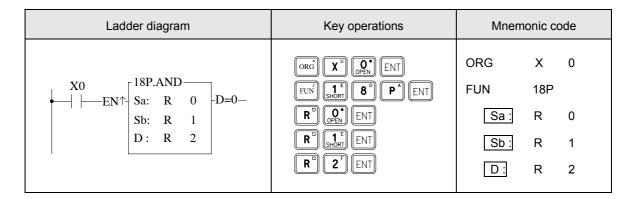

Sa: The register to be ANDed Sb: The register to be ANDed

D : The register to store the result of AND The Sa, Sb, D may combine with V, Z to serve indirect addressing application

| Range     | WX    | WY        | WM         | WS    | TMR  | CTR  | HR    | IR    | OR    | HR    | HSCR  | RTCR      | SR        | ROR   | DR    | K         |

|-----------|-------|-----------|------------|-------|------|------|-------|-------|-------|-------|-------|-----------|-----------|-------|-------|-----------|

| Ono       | WX0   | WY0       | WM0        | WS0   | T0   | C0   | R0    | R3804 | R3904 | R3920 | R4096 | R4128     | R4136     | R5000 | D0    | 16/32 bit |

| Ope-\rand | WX240 | <br>WY240 | <br>WM1896 | WS984 | T255 | C255 | R3839 | R3903 | R3919 | R4047 | R4127 | <br>R4135 | <br>R4167 | R8071 | D3071 | +/-number |

| Sa        | 0     | 0         | 0          | 0     | 0    | 0    | 0     | 0     | 0     | 0     | 0     | 0         | 0         | 0     | 0     | 0         |

| Sb        | 0     | 0         | 0          | 0     | 0    | 0    | 0     | 0     | 0     | 0     | 0     | 0         | 0         | 0     | 0     | 0         |

| D         |       | 0         | 0          | 0     | 0    | 0    | 0     |       | 0     | 0     | 0     | 0         | <b>O*</b> | O*    | 0     |           |

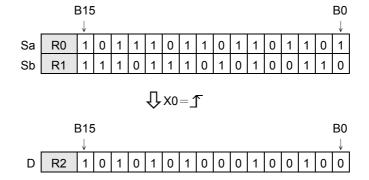

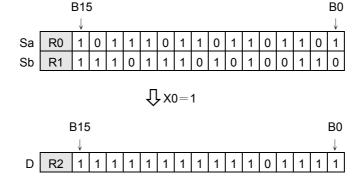

Performs logical AND operation for the data of Sa and Sb when the operation control input "EN" =1 or "EN↑" (☐ instruction) from 0 to 1. This operation compares the corresponding bits of Sa and Sb (B0~B15 or B0~B31). The bit in the D is set to 1 if both of the corresponding bits data of Sa and Sb is 1. The bit in the D is set to 0 if one of the corresponding bits is 0.

### Example Operation of 16-bit logical AND

#### <u>Ladder symbol</u> <u>Operand</u>

Sa: The register to be ORed Sb: The register to be ORed

D : The register to store the result of OR

The Sa, Sb, D may combine with V, Z to serve indirect addressing

| Range        | WX                | WY                | WM                 | WS                | TMR             | CTR             | HR               | IR | OR | HR | HSCR | RTCR                | SR | ROR       | DR               | K                      |

|--------------|-------------------|-------------------|--------------------|-------------------|-----------------|-----------------|------------------|----|----|----|------|---------------------|----|-----------|------------------|------------------------|

| Ope-<br>rand | WX0<br> <br>WX240 | WY0<br> <br>WY240 | WM0<br> <br>WM1896 | WS0<br> <br>WS984 | T0<br> <br>T255 | C0<br>-<br>C255 | R0<br> <br>R3839 |    |    |    |      | R4128<br> <br>R4135 |    |           | D0<br> <br>D3071 | 16/32 bit<br>+/-number |

| Sa           | 0                 | 0                 | 0                  | 0                 | 0               | 0               | 0                | 0  | 0  |    | 0    | 0                   | 0  | 0         | 0                | 0                      |

| Sb           | 0                 | 0                 | 0                  | 0                 | 0               | 0               | 0                | 0  | 0  |    | 0    | 0                   | 0  | 0         | 0                | 0                      |

| D            |                   | 0                 | 0                  | 0                 | 0               | 0               | 0                |    | 0  |    | 0    | 0                   | O* | <b>O*</b> | 0                |                        |

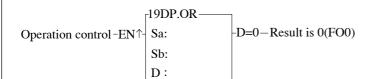

Performs logical OR operation for the data of Sa and Sb when the operation control input "EN" =1 or "EN↑" (☐ instruction) from 0 to 1. This operation compares the corresponding bits of Sa and Sb (B0~B15 or B0~B31). The bit in the D is set to 1 if one of the corresponding of Sa or Sb is 1. The bit in the D is set to 0 if both of the corresponding bits of Sa and Sb is 0.

Example Operation of 16-bit logical OR

| Ladder diagram | Key operations                                                          | Mnemonic code                         |

|----------------|-------------------------------------------------------------------------|---------------------------------------|

| X0             | ORG X OPEN ENT  FUN SHORT 9 ENT  R OPEN ENT  R ENT  R ENT  R ENT  R ENT | ORG X 0 FUN 19 Sa: R 0 Sb: R 1 D: R 2 |

FUN 20 **D** P →BCD

#### BIN TO BCD CONVERSION

(Converts BIN data of the device specified at S into BCD and stores the result in D)

FUN 20 **D P** →BCD

#### Ladder symbol

# Conversion control -EN $\uparrow$ $\begin{array}{c} 20DP. \rightarrow BCD \\ S: \\ D: \end{array}$ -ERR- Error(FO0)

#### Operand

- S: The register to be converted

- D : The register to store the converted data (BCD code)

The S, D may combine with V, Z to serve indirect addressing

| Range  | WX    | WY    | WM     | WS    | TMR  | CTR  | HR    | IR    | OR    | HR    | HSCR  | RTCR  | SR    | ROR   | DR    | K          |

|--------|-------|-------|--------|-------|------|------|-------|-------|-------|-------|-------|-------|-------|-------|-------|------------|

|        | WX0   | WY0   | WM0    | WS0   | T0   | C0   | R0    | R3804 | R3940 | R3920 | R4096 | R4128 | R4136 | R5000 | D0    | 16/32 bit  |

| Ope-\  |       |       |        |       |      |      |       |       |       |       |       |       |       |       |       | +/- number |

|        |       |       |        |       |      |      |       |       |       |       |       |       |       |       |       |            |

| rand \ | WX240 | WY240 | WM1896 | WS984 | T255 | C255 | R3839 | R3903 | R3919 | R4047 | R4127 | R4135 | R4167 | R8071 | D3071 | ·/ Hambon  |

| rand \ | WX240 | WY240 | WM1896 | WS984 | T255 | C255 | R3839 | R3903 | R3919 | R4047 | R4127 | R4135 | R4167 | R8071 | D3071 |            |

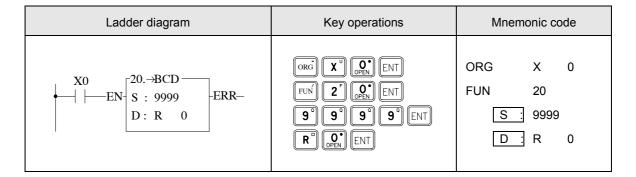

- FB-PLC uses binary code to store and to execute calculations. If want to send the internal PLC data to the external displays such as seven-segment displays, it is more convenient for us to read the result on screen by converting the BIN data to BCD data. For example, it is more clear for us to read the reading "12" instead of the binary code "1100."

- Converts BIN data of the device specified at S into BCD and writes the result in D when the operation control input "EN" =1 or "EN↑" (☐ instruction) from 0 to 1. If the data in S is not a BCD value (0~9999 or 0~9999999), then the error flag FO0 is set to 1 and the old data of D are retained.

Example

16-bit BIN to BCD conversion

FUN 21 D ☐ BCD TO BIN CONVERSION

→BIN

BCD TO BIN CONVERSION

(Converts BCD data of the device specified at S into BIN and stores the result in D)

→BIN

#### Ladder symbol

#### Operand

S: The register to be converted

D : The register to store the converted data (BIN code)

The S, D may combine with V, Z to serve indirect addressing

| Range  | WX    | WY    | WM     | WS    | TMR  | CTR  | HR    | IR    | OR    | HR    | HSCR  | RTCR  | SR    | ROR   | DR    |

|--------|-------|-------|--------|-------|------|------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

|        | WX0   | WY0   | WM0    | WS0   | T0   | C0   | R0    | R3840 | R3904 | R3920 | R4096 | R4128 | R4136 | R5000 | D0    |

| Ope-\  |       |       |        |       |      |      |       |       |       |       |       |       |       |       |       |

| rand \ | WX240 | WY240 | WM1896 | WS984 | T255 | C255 | R3839 | R3903 | R3919 | R4047 | R4127 | R4135 | R4167 | R8071 | D3071 |

|        |       |       |        |       |      |      |       |       |       |       |       |       |       |       |       |

| S      | 0     | 0     | 0      | 0     | 0    | 0    | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

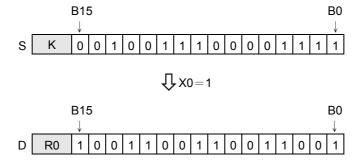

- The decimal (BCD) data must be converted to binary (BIN) data first in order for PLC to accept the data which is originally in decimal unit (BCD code) inputted from external device such as digital switch because the BCD data can not be accepted by PLC for its operations.

- Converts BCD data of the device specified at S into BIN and writes the result in D when the operation control input "EN" =1 or "EN↑" ( instruction) from 0 to 1. If the data in S is not in BCD, then the error flag FO0 is set to 1 and the old data of D are retained.

- Constant is converted to BIN automatically when store in program and can not be used as a source operand of this function.

#### Example

#### 16-bit BCD to BIN conversion