## **Chapter 9 Advanced Application Instructions**

| • | Arithmetical operation instructions     | (FUN23~30) ·····9-2     | $\sim$ | 9-9   |

|---|-----------------------------------------|-------------------------|--------|-------|

| • | Logical operation instructions          | (FUN35~36)9-10          | ~      | 9-11  |

| • | Comparison instructions                 | (FUN37) ·····9-12       |        |       |

| • | Data movement instructions              | (FUN40~48) ·····9-13    | ~      | 9-21  |

| • | Shifting/Rotating instructions          | (FUN51~54) ·····9-22    | ~      | 9-25  |

| • | Code conversion instructions            | (FUN57~64)9-26          | ~      | 9-38  |

| • | Flow control instructions               | (FUN65~71)9-39          | ~      | 9-46  |

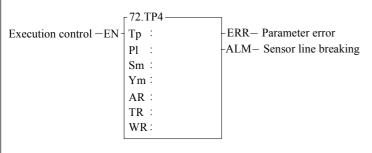

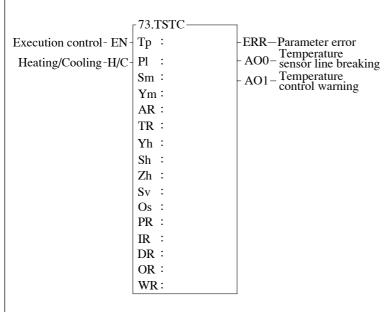

| • | Temperature control instructions 1      | (FUN72~73) ·····9-47    | ~      | 9-48  |

| • | I/O instructions                        | (FUN74~84) ·····9-49    | ~      | 9-62  |

| • | Temperature control instructions 2      | (FUN85~86)9-63          | ~      | 9-64  |

| • | Cumulative timer instructions           | (FUN87~89)9-65          | ~      | 9-66  |

| • | Watchdog timer instructions             | (FUN90~91)9-67          | ~      | 9-68  |

| • | High speed counting/timing instructions | (FUN92~93)9-69          | ~      | 9-70  |

| • | Report printing instructions            | (FUN94)9-71             | ~      | 9-72  |

| • | Slow up/Slow down instructions          | (FUN95)9-73             | ~      | 9-74  |

| • | Communication instructions              | (FUN96~97) ·····9-75    | ~      | 9-76  |

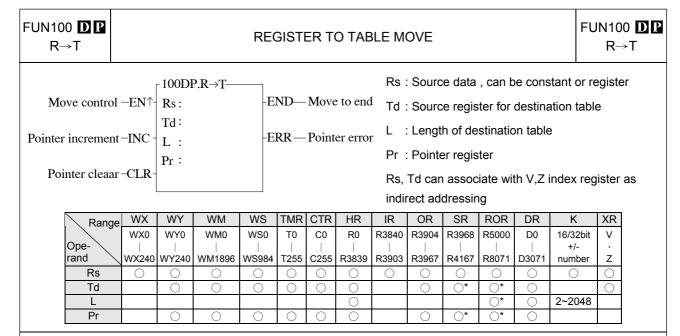

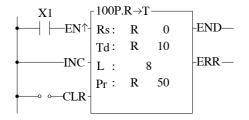

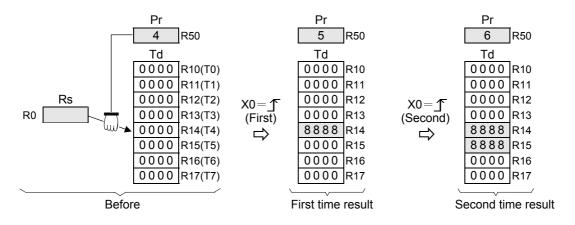

| • | Table instructions                      | (FUN100~113)9-77        | $\sim$ | 9-94  |

| • | Matrix instructions                     | (FUN120~130)9-95        | ~      | 9-106 |

| • | NC position instructions                | (FUN140~143)9-107       | ~      | 9-110 |

| • | Interrupt control instructions          | (FUN145~146) ·····9-111 | ~      | 9-112 |

|   |                                         |                         |        |       |

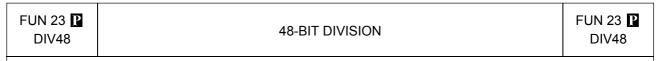

#### Arithmetical operation instructions

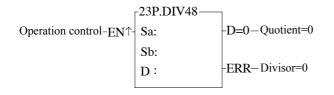

Sa: Starting register of dividend Sb: Starting register of divisor

D : Starting register for storing the division result

(quotient)

Sa, Sb, can combine V,Z for index addressing.

| Range        | HR      | OR      | SR      | ROR     | DR      | XR      |

|--------------|---------|---------|---------|---------|---------|---------|

| _            | R0      | R3904   | R3968   | R5000   | D0      | ٧       |

| Ope-<br>rand |         |         |         |         |         | ` `     |

| rand         | R3839   | R3967   | R4167   | R8071   | D3071   | Z       |

| Sa           | 0       | 0       | 0       | 0       | 0       | 0       |

| Sb           | $\circ$ | $\circ$ | $\circ$ | $\circ$ | $\circ$ | $\circ$ |

| D            | 0       | 0       | O*      | O*      | 0       | 0       |

- When operation control "EN"=1 or "EN↑" (☐ instruction) changes from 0→1, will perform the 42 bits division operation. Dividend and divisor are each formed by three consecutive registers starting by Sa and Sb respectively. If the result is zero, 'D=0' output will be set to 1. If divisor is zero then the 'ERR' will be set to 1 and the resultant register will keep unchanged.

- All operands involved in this function are all 42 bits, so Sa, Sb and D are all comprised by 3 consecutive registers.

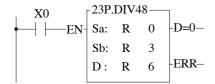

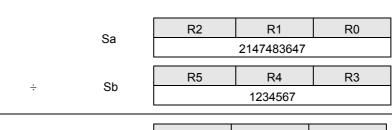

#### Example: 48-bit division

In this example dividend formed by register R2, R1, R0 will be divided by divisor formed by register R5, R4, R3. The quotient will store in R8, R7, and R6.

| R8 | R7   | R6 |

|----|------|----|

|    | 1739 |    |

Quotient

## FUN 24 DP SUM (Summation of block data) FUN 24 DP SUM

Operation control-EN  $\uparrow$  S: N: D:

S : Starting number of source register

N : Number of registers to be summed (successive N data units starting from S)

D: The register which stored the result (summation)

S, N, D, can associate with V, Z index register to serve the indirect addressing application.

| Range        | WX      | WY      | WM      | WS    | TMR     | CTR     | HR      | IR    | OR    | SR    | ROR       | DR      | K   | XR |

|--------------|---------|---------|---------|-------|---------|---------|---------|-------|-------|-------|-----------|---------|-----|----|

|              | WX0     | WY0     | WM0     | WS0   | T0      | C0      | R0      | R3840 | R3904 | R3968 | R5000     | D0      | 1   | V  |

| Ope-<br>rand |         |         |         |       |         |         |         |       |       |       |           |         |     | `  |

| rand         | WX240   | WY240   | WM1896  | WS984 | T255    | C255    | R3839   | R3903 | R3967 | R4167 | R8071     | D3071   | 511 | Z  |

| S            | $\circ$ | $\circ$ | 0       | 0     | $\circ$ | $\circ$ | $\circ$ | 0     | 0     | 0     | 0         | $\circ$ |     | 0  |

| N            | 0       | 0       | $\circ$ | 0     | 0       | 0       | 0       | 0     | 0     | 0     | 0         | 0       | 0   | 0  |

| D            |         | 0       | 0       | 0     | 0       | 0       | 0       |       | 0     | O*    | <b>O*</b> | 0       |     | 0  |

- When operation control "EN"=1 or "EN ↑" ( instruction) changes from 0→1, it puts the successive N units of 16bit or 32 bit ( instruction) registers for addition calculation to get the summation, and stores the result into the register which is designated by D.

- When the value of N is 0 or greater than 511, the operation will not be performed.

- Communication port1 or port2 can be used to serve as a general purpose ASCII communication interface. If the data error detecting method is Check-Sum, this instruction can be used to generate the sum value for sending data or ot use this instruction to check if the received data is error or not.

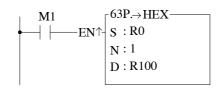

⟨ Example 1 ⟩ When M1 changes from OFF→ON, following instruction will calculates the summation for 16-bit data.

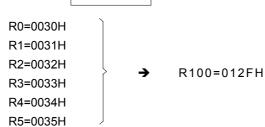

The left illustrates that 6 16-bit registers starting from R0 is calculated for summation, and the result is stored into the R100 register.

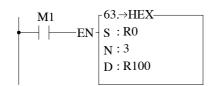

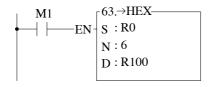

$\langle$  Example 2  $\rangle$  When M1 is ON, it calculates the summation for 32-bit data.

The left illustrates that three 32-bit registers starting from DR0, is calculated for their summation, and the result is stored into the DR100 register.

R1 · R0=00310030H R3 · R2=00330032H R5 · R4=00410039H

#### Arithmetical operation instructions

FUN 25 DP MEAN (Average of the block data) FUN 25 DP MEAN

Operation control-EN  $\uparrow$  S: ERR—N range error N: D:

S : Source register number

N : Number of registers to be averaged (N units of successive registers starting from S)

D : Register number for storing result (mean value)

The S, N, D may combine with V, Z to serve indirect address application

| Range        | WX      | WY    | WM     | WS      | TMR  | CTR     | HR    | IR    | OR    | SR        | ROR   | DR    | K       | XR      |

|--------------|---------|-------|--------|---------|------|---------|-------|-------|-------|-----------|-------|-------|---------|---------|

|              | WX0     | WY0   | WM0    | WS0     | T0   | C0      | R0    | R3840 | R3904 | R3968     | R5000 | D0    | 2       | V       |

| Ope-<br>rand |         |       |        |         |      |         |       |       |       |           |       |       |         | `       |

| rand         | WX240   | WY240 | WM1896 | WS984   | T255 | C255    | R3839 | R3903 | R3967 | R4167     | R8071 | D3071 | 256     | Z       |

| S            | $\circ$ | 0     | 0      | $\circ$ | 0    | $\circ$ | 0     | 0     | 0     | 0         | 0     | 0     |         | $\circ$ |

| N            | 0       | 0     | 0      | $\circ$ | 0    | 0       | 0     | 0     | 0     | 0         | 0     | 0     | $\circ$ | 0       |

| D            |         | 0     | 0      | 0       | 0    | 0       | 0     |       | 0     | <b>O*</b> | O*    | 0     |         | 0       |

- When operation control "EN" = 1 or "EN↑" (☐ instruction) from 0 to 1, add the N successive 16-bit or 32-bit (☐ instruction) numerical values starting from S, and then divided by N. Store this mean value (rounding off numbers after the decimal point) in the register specified by D.

- While the N value is derived from the content of the register, if the N value is not between 2 and 256, then the N range error "ERR" will be set to 1, and do not execute the operation.

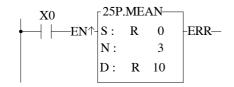

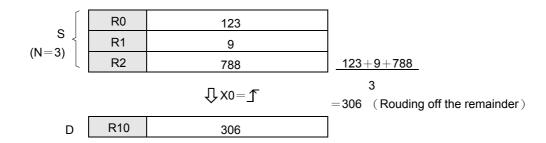

At left, the example program gets the mean value of the 3 successive 16-bit registers starting from R0, and stores the results into the 16-bit register R10

FUN 26 DP SQRT SQUARE ROOT FUN 26 DP SQRT

Operation control -EN $\uparrow$ - S: D: -ERR— S range error

- S : Source register to be taken square root

- D : Register for storing result (square root value)

- S, D may combine with V, Z to serve indirect address application

| Range  | WX    | WY    | WM     | WS    | TMR  | CTR  | HR    | IR    | OR    | SR    | ROR   | DR    | K         | XR |

|--------|-------|-------|--------|-------|------|------|-------|-------|-------|-------|-------|-------|-----------|----|

|        | WX0   | WY0   | WM0    | WS0   | T0   | C0   | R0    | R3840 | R3904 | R3968 | R5000 | D0    | 16/32-bit | V  |

| Ope-   |       |       |        |       |      |      |       |       |       |       |       |       | 10/32-010 | `  |

| rand   |       |       |        |       |      |      |       |       |       |       |       |       |           | -  |

| Ianu \ | WX240 | WY240 | WM1896 | WS984 | T255 | C255 | R3839 | R3903 | R3967 | R4167 | R8071 | D3071 |           |    |

| S      | WX240 | WY240 | WM1896 | WS984 | T255 | C255 | R3839 | R3903 | R3967 | R4167 | R8071 | D3071 | 0         | 0  |

- When operation control "EN" = 1 or "EN↑" (☐ instruction) from 0 to 1, take the square root (rounding off numbers after the decimal point) of the data specified by the S field, and store the result into the register specified by D.

- While the S value is derived from the content of the register, if the value is negative, then the S value error flag "ERR" will be set to 1, and do not execute the operation.

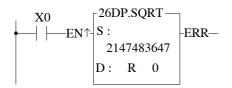

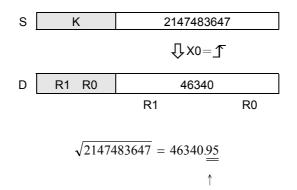

• The instruction at left calculates the square root of the constant 2147483647, and stores the result in R0.

rounding off

#### Arithmetical operation instructions

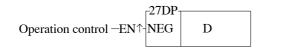

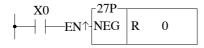

# FUN 27 DP NEGATION (Take the negative value) FUN 27 DP NEG

D : Register to be negated D may combine with V, Z to serve indirect address application

| Range | WY    | WM     | WS    | TMR  | CTR  | HR    | OR    | SR    | ROR   | DR    | XR |

|-------|-------|--------|-------|------|------|-------|-------|-------|-------|-------|----|

|       | WY0   | WM0    | WS0   | T0   | C0   | R0    | R3904 | R3968 | R5000 | D0    | V  |

| Ope-  |       |        |       |      |      |       |       |       |       |       | `  |

| rand  | WY240 | WM1896 | WS984 | T255 | C255 | R3839 | R3967 | R4167 | R8071 | D3071 | Z  |

| D     | 0     | 0      | 0     | 0    | 0    | 0     | 0     | O*    | O*    | 0     | 0  |

- When operation control "EN" = 1 or "EN ↑" ( instruction) from 0 to 1, negate (ie. calculate 2's complement) the value of the content of the register specified by D, and store it back in the original D register.

- If the value of the content of D is negative, then the negation operation will make it positive.

• The instruction at left negates the value of the R0 register, and stores it back to R0.

| D | R0 | 12345                    | ☞3039H             |

|---|----|--------------------------|--------------------|

|   |    | <b>1</b> X0 = <b>1</b> ✓ |                    |

| D | R0 | -12345                   | <sup>©</sup> CFC7H |

FUN 28 DP ABSOLUTE

ABS (Take the absolute value)

FUN 28 DP ABS

Operation control –EN↑ ABS D

D : Register to be taken absolute value

D may combine with V, Z to serve indirect address application

| Range | WY    | WM     | WS    | TMR  | CTR  | HR    | OR    | SR        | ROR       | DR    | XR |

|-------|-------|--------|-------|------|------|-------|-------|-----------|-----------|-------|----|

|       | WY0   | WM0    | WS0   | T0   | C0   | R0    | R3904 | R3968     | R5000     | D0    | ٧  |

| Ope-  |       |        |       |      |      | 1     |       |           |           |       |    |

| rand  | WY240 | WM1896 | WS984 | T255 | C255 | R3839 | R3967 | R4167     | R8071     | D3071 | Z  |

| D     | 0     | 0      | 0     | 0    | 0    | 0     | 0     | <b>O*</b> | <b>O*</b> | 0     | 0  |

• When operation control "EN" = 1 or "EN↑" (☐ instruction) from 0 to 1, calculate the absolute value of the content of the register specified by D, and write it back into the original D register.

• The instruction at left calculates the absolute value of the R0 register, and stores it back in R0.

D R1 R0 -12345 © CFC7H

$\int X0 = \int$

R1 R0 12345 \$\square\$ 3039H

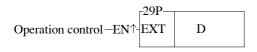

| FUN 29 P<br>EXT | SIGN EXTENSION | FUN 29 P<br>EXT |

|-----------------|----------------|-----------------|

|                 |                |                 |

D : Register to be taken sign extension

D may combine with V, Z to serve indirect address application

| Range | WY    | WM     | WS    | TMR  | CTR  | HR    | OR    | SR    | ROR   | DR    | XR |

|-------|-------|--------|-------|------|------|-------|-------|-------|-------|-------|----|

|       | WY0   | WM0    | WS0   | T0   | C0   | R0    | R3904 | R3968 | R5000 | D0    | V  |

| Ope-  |       |        |       |      |      |       |       |       |       |       | `  |

| rand  | WY240 | WM1896 | WS984 | T255 | C255 | R3839 | R3967 | R4167 | R8071 | D3071 | Z  |

| D     | 0     | 0      | 0     | 0    | 0    | 0     | 0     | O*    | O*    | 0     | 0  |

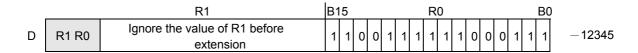

- When operation control "EN" = 1 or "EN↑" (P instruction) from 0 to 1, this instruction will sign extent the 16 bit numerical value specified by D to 32-bit value and store it into the 32-bit register comprised by the two successive words, D + 1 and D. (Both values are the same, only it was originally formated as a 16 bit numerical value, and was then extended to be formated as a 32 bit numerical value.)

- This instruction extent the numerical value of a 16-bit register into an equivalent numerical value in a 32-bit register (for example 33FFH converts to 000033FFH), Its main function is for numerical operations (+,-,\*,/,CMP......) which can take the 16 bit or 32 bit numerical values as operand. Before operation all the operand should be adjusted to the same length for proper operation.

$$\begin{array}{c|c} X0 \\ \hline \end{array} = EN \uparrow \begin{array}{c|c} 29P \\ \hline \end{array} = R \quad 0$$

The instruction at left takes a 16 bit numerical value R0, and extends it to an equivalent value in 32 bits, then stores it into a 32 bit register (DR0=R1R0) comprised R0 and R1

Fill B15 value into B31-B16,(if B15 is 0, then B31-B16 are all 0)

Before extension (16 bits) R0= CFC7H=-12345

After extension (32 bits) R1R0=FFFFCFC7H=-12345

The two numerical values are actually the same

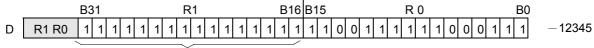

| FUN 30 | General purpose PID operation | FUN 30 |

|--------|-------------------------------|--------|

| PID    | (Brief description)           | PID    |

parameter table comprised by 8 consecutive registers.

SR : Starting register of process control

Ts : PID Operation time interval

OR: PID output register

PR : Starting register of the process parameter table comprised by 7 consecutive registers.

WR: Starting register of working variable for PID internal operation. It requires 7 registers and can't be re-used in other part of the ladder program.

- PID function according to the current value of process variable (PV) derived from the external analog signal and the setting value (SP) of process performs the calculation, which base on the PID formula. The result of calculation is the control output for the controlled process, which can feed directly to the AO module or other output interface or leaved for further process. The usage of PID control for process if properly can achieve a fast and smooth result of PV tracking toward SP change or immune to the disturbance of process.

- The PID formula in digital form:

$$Mn = [(1000/Pb) \times En] + \sum_{0}^{n} [(1000/Pb) \times Ti \times Ts \times En] - [(1000/Pb) \times Td \times (PVn-PVn-1)/Ts] + Bias$$

Mn : Control output at time "n"

Pb : Proportional band (range: 2~5000, unit 0.1%. Kc (gain) =1000/ Pb)

Ti : Intergal time constant ( range : 0~9999 corresponds to 0.00~99.99 Repeats/Minute )

Td : Differential time constant (range: 0~9999 corresponds to 0.00~99.99 Minutes)

PVn : Process value at time "n"

PV n-1 : Process value at time "n"

En :Error at time "n" =set value (SP) – process value at time "n" (PVn)

Ts : Interval time of PID calculation (range: 1~3000, unit: 0.01 S)

Bias : Control output offset ( range: 0~4095 )

• For detail description of this function, please refer chapter 21.

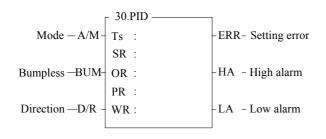

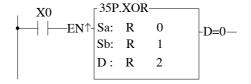

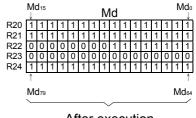

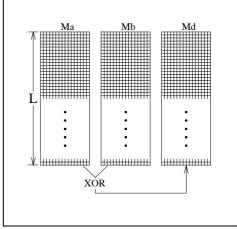

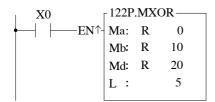

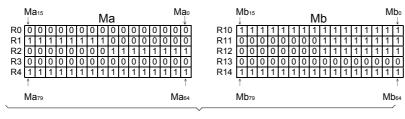

FUN 35 DP XOR EXCLUSIVE OR XOR

Operation control -EN  $\uparrow$  Sa: Sb: D:

Sa: Source data a for exclusive or operation

Sb: Source data b for exclusive or operation

D: Register storing XOR results

Sa, Sb, D may combine with V, Z to serve indirect address application

| Range        | WX      | WY    | WM      | WS      | TMR     | CTR     | HR    | IR    | OR    | SR    | ROR   | DR    | K        | XR      |

|--------------|---------|-------|---------|---------|---------|---------|-------|-------|-------|-------|-------|-------|----------|---------|

| _ \          | WX0     | WY0   | WM0     | WS0     | T0      | C0      | R0    | R3840 | R3904 | R3968 | R5000 | D0    | 16/32bit | ٧       |

| Ope-<br>rand |         |       |         |         |         |         |       |       |       |       |       |       | +/-      | `       |

| rand         | WX240   | WY240 | WM1896  | WS984   | T255    | C255    | R3839 | R3903 | R3967 | R4167 | R8071 | D3071 | number   | Z       |

| Sa           | $\circ$ | 0     | $\circ$ | $\circ$ | $\circ$ | $\circ$ | 0     | 0     | 0     | 0     | 0     | 0     | $\circ$  | $\circ$ |

| Sb           | 0       | 0     | 0       | 0       | 0       | 0       | 0     | 0     | 0     | 0     | 0     | 0     | 0        | 0       |

| D            |         |       | 0       | 0       | 0       |         | 0     |       | 0     | O*    | O*    | 0     |          | 0       |

- When operation control "EN" = 1 or "EN↑" (☐ instruction) changes from 0 to 1, will perform the logical XOR (exclusive or) operation of data Sa and Sb. The operation of this function is to compare the corresponding bits of Sa and Sb (B0~B15 or B0~B31), and if bits at the same position have different status, then set the corresponding bit within D as 1, otherwise as 0.

- After the operation, if all the bits in D are all 0, then set the 0 flag "D = 0" to 1.

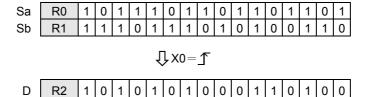

The instruction at left makes a logical XOR operation using the R0 and R1 registers, and stores the result in R2.

$$\Omega = \mathbb{Z}$$

D R2 0 1 0 1 0 1 0 1 1 1 0 0 1 0 1 1

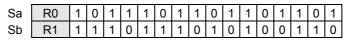

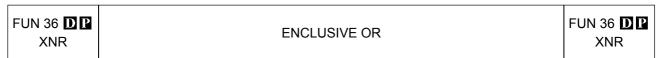

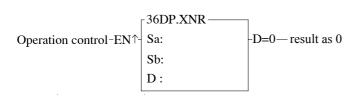

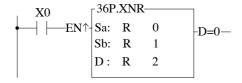

Sa: Data a for XNR operation

Sb: Data b for XNR operation

D: Register storing XNR results

Sa, Sb, D may combine with V, Z to serve indirect address application

| Range        | WX                | WY                | WM                 | WS                | TMR             | CTR             | HR               | IR                  | OR                  | SR | ROR | DR | K                     | XR     |

|--------------|-------------------|-------------------|--------------------|-------------------|-----------------|-----------------|------------------|---------------------|---------------------|----|-----|----|-----------------------|--------|

| Ope-<br>rand | WX0<br> <br>WX240 | WY0<br> <br>WY240 | WM0<br> <br>WM1896 | WS0<br> <br>WS984 | T0<br> <br>T255 | C0<br> <br>C255 | R0<br> <br>R3839 | R3840<br> <br>R3903 | R3904<br> <br>R3967 |    |     |    | 16/32-bit<br>± number | V<br>Z |

| Sa           | 0                 | 0                 | 0                  | 0                 | 0               | 0               | 0                | 0                   | 0                   | 0  | 0   | 0  | 0                     | 0      |

| Sb           | 0                 | 0                 | 0                  | 0                 | 0               | 0               | 0                | 0                   | 0                   | 0  | 0   | 0  | 0                     | 0      |

| D            |                   | 0                 | 0                  | 0                 | 0               | 0               | 0                |                     | 0                   | O* | O*  | 0  |                       | 0      |

- When operation control "EN" = 1 or "EN↑" (☐ instruction) changes from 0 to 1, will perform the logical XNR (inclusive or) operation of data Sa and Sb. The operation of this function is to compare the corresponding bits of Sa and Sb (B0~B15 or B1~B31), and if the bit has the same value, then set the corresponding bit within D as 1. If not then set it to 0.

- After the operation, if the bits in D are all 0, then set the 0 flag "D=0" to 1.

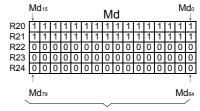

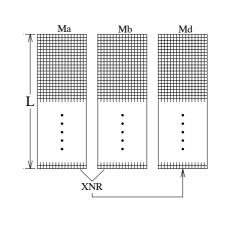

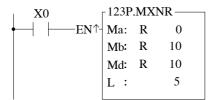

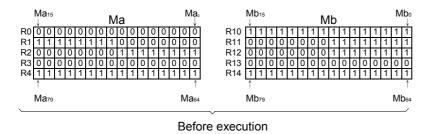

The instruction at left makes a logical XNR operation of the R0 and R1 registers, and the results are stored in the R2 register.

|   | Range        | WX    | WY    | WM     | WS    | TMR  | CTR  | HR    | IR    | OR    | SR    | ROR   | DR    | K             | XR      |

|---|--------------|-------|-------|--------|-------|------|------|-------|-------|-------|-------|-------|-------|---------------|---------|

|   | 0:           | WX0   | WY0   | WM0    | WS0   | T0   | C0   | R0    | R3840 | R3904 | R3968 | R5000 | D0    | 16/32-bit     | V       |

|   | Ope-<br>rand | WX240 | WY240 | WM1896 | WS984 | T255 | C255 | R3839 | R3903 | R3967 | R4167 | R8071 | D3071 | +/-<br>number | ž       |

| Ì | S            | 0     | 0     | 0      | 0     | 0    | 0    | 0     | 0     | 0     | 0     | 0     | 0     |               | $\circ$ |

|   | SU           | 0     | 0     | 0      | 0     | 0    | 0    | 0     | 0     | 0     | 0     | 0     | 0     | 0             | $\circ$ |

|   | SL           | 0     | 0     | 0      | 0     | 0    | 0    | 0     | 0     | 0     | 0     | 0     | 0     | 0             |         |

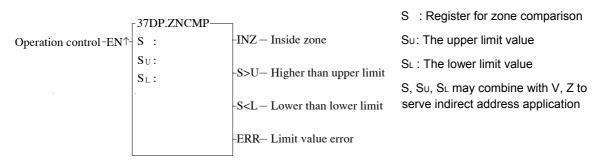

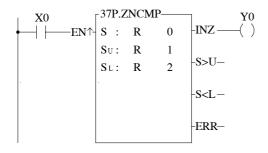

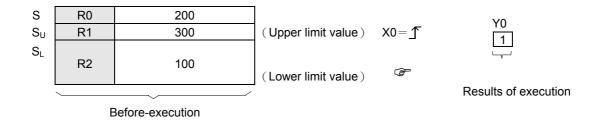

- When operation control "EN" = 1 or "EN  $\uparrow$ " ( $\blacksquare$  instruction) changes from 0 to 1, compares S with upper limit S<sub>U</sub> and lower limit S<sub>L</sub>. If S is between the upper limit and the lower limit ( $S_L \le S \le S_U$ ), then set the inside zone flag "INZ" to 1. If the value of S is greater than the upper limit S<sub>U</sub>, then set the higher than upper limit flag "S>U" to 1. If the value of S is smaller then the lower limit S<sub>L</sub>, then set the lower than lower limit flag "S<L" as 1.

- The upper limit  $S_U$  should be greater than the lower limit  $S_L$ . If  $S_U < S_L$ , then the limit value error flag "ERR" will set to 1, and this instruction will not carry out.

- The instruction at left compares the value of R0 with the upper and lower limit zones formed by R1 and R2. If the values of R0~R2 are as shown in the diagram at bottom left, then the result can then be obtained as at the right of this diagram.

- If want to get the status of out side the zone, then OUT NOT Y0 may be used, or an OR operation between the two outputs S>U and S<L may be carried out, and move the result to Y0.

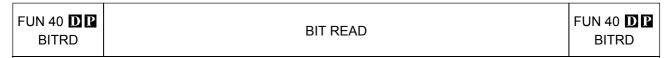

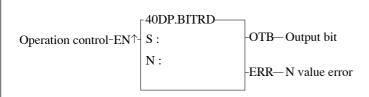

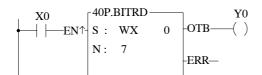

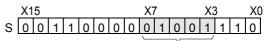

S: Source data to be read

N: The bit number of the S data to be read out.

S, N may combine with V, Z to serve indirect address application

| Range        | WX    | WY    | WM     | WS    | TMR  | CTR  | HR    | IR    | OR    | SR        | ROR   | DR    | K          | XR       |

|--------------|-------|-------|--------|-------|------|------|-------|-------|-------|-----------|-------|-------|------------|----------|

|              | WX0   | WY0   | WM0    | WS0   | T0   | C0   | R0    | R3840 | R3904 | R3968     | R5000 | D0    | 16/32-bit  | <b>V</b> |

| Ope-<br>rand | WX240 | WY240 | WM1896 | WS984 | T255 | C255 | R3839 | R3903 | R3967 | <br>R4167 | R8071 | D3071 | +/- number | 、<br>7   |

|              |       |       |        |       |      |      |       |       |       |           |       |       |            |          |

| S            | 0     | 0     | 0      | 0     | 0    | 0    | 0     | O     | 0     | 0         | 0     | 0     | 0          | 0        |

- When read control "EN" = 1 or "EN↑" ( instruction) changes from 0 to 1, take the Nth bit of the S data out, and put it to the output bit "OTB".

- When read control "EN" = 0 or "EN ↑" ( instruction) is not change from 0 to 1, The output "OTB" can be selected to keep at the last state( if M1919=0 ) or set to zero ( if M1919=1 ).

- When the operand is 16 bit, the effective range for N is 0~15. For 32 bit operand ( instruction) it is 0~31. N beyond this range will set the N value error flag "ERR" to 1, and do not carry out this instruction.

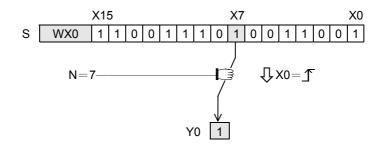

The instruction at left reads the 7th bit (X7) status from WX0 (X0~X15) and output to Y0. The results are as follows:

#### Data movement instructions

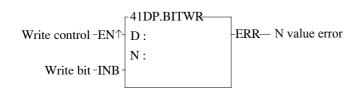

# FUN 41 DP BITWR BITWR BITWR

D : Register for bit write

N : The bit number of the D register to be written.

D, N may combine with V, Z to serve indirect address application

| Range  | WX    | WY    | WM     | WS    | TMR  | CTR  | HR    | IR    | OR    | SR    | ROR   | DR    | K     | XR |

|--------|-------|-------|--------|-------|------|------|-------|-------|-------|-------|-------|-------|-------|----|

|        | WX0   | WY0   | WM0    | WS0   | T0   | C0   | R0    | R3840 | R3904 | R3968 | R5000 | D0    | 0 0   | ٧  |

| Ope-   |       |       |        |       |      |      |       |       |       |       |       |       | or    | `  |

| . \    |       |       |        |       |      |      |       |       |       |       |       |       |       |    |

| rand   | WX240 | WY240 | WM1896 | WS984 | T255 | C255 | R3839 | R3903 | R3967 | R4167 | R8071 | D3071 | 15 31 | Z  |

| rand \ | WX240 | WY240 | WM1896 | WS984 | T255 | C255 | R3839 | R3903 | R3967 | R4167 | R8071 | D3071 | 15 31 | Z  |

- When write control "EN" = 1 or "EN ↑" ( instruction) changes from 0 to 1, will write the write bit (INB) into the Nth bit of register D.

- When the operand is 16 bit, the effective range of N is 0~15. For 32 bit ( instruction) operand it is 0~31. N beyond this range, will set the N value error flag "ERR" to 1, and do not carry out this instruction.

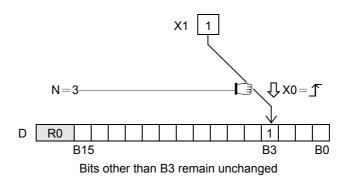

The instruction at left writes the status of the write bit INB into B3 of R0. Assuming

X1 = 1, the result will be as follows:

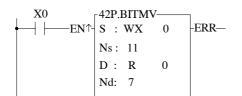

FUN 42 **DP**BITMV

BIT MOVE

FUN 42 **DP**BITMV

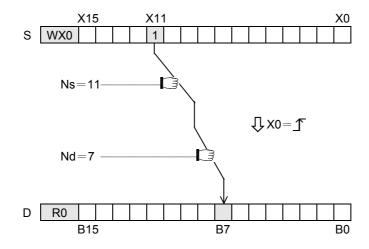

S : Source data to be moved

Ns: Assign Ns bit within S as source bit

D: Destination register to be moved

Nd: Assign Nd bit within D as target bit

S, Ns, D, Nd may combine with V, Z to serve indirect address application

| Move control -EN↑- | 42DP.BITMV<br>S : | -ERR— N value error |

|--------------------|-------------------|---------------------|

|                    | Ns:               |                     |

|                    | D :               |                     |

|                    | Nd:               |                     |

|                    |                   |                     |

| Range | WX      | WY      | WM      | WS      | TMR     | CTR  | HR      | IR    | OR    | SR      | ROR     | DR      | K          | XR      |

|-------|---------|---------|---------|---------|---------|------|---------|-------|-------|---------|---------|---------|------------|---------|

|       | WX0     | WY0     | WM0     | WS0     | T0      | C0   | R0      | R3840 | R3904 | R3968   | R5000   | D0      | 16/32-bit  | V       |

| Ope-  |         |         |         |         |         |      |         |       |       |         |         |         | +/- number | ` `     |

| rand  | WX240   | WY240   | WM1896  | WS984   | T255    | C255 | R3839   | R3903 | R3967 | R4167   | R8071   | D3071   | ,          | Z       |

| S     | $\circ$ | $\circ$ | $\circ$ | $\circ$ | $\circ$ | 0    | $\circ$ | 0     | 0     | $\circ$ | $\circ$ | $\circ$ | $\circ$    | $\circ$ |

| Ns    | 0       | 0       | 0       | 0       | 0       | 0    | 0       | 0     | 0     | 0       | 0       | 0       | 0~31       | 0       |

| D     |         | 0       | 0       | 0       | 0       | 0    | 0       |       | 0     | O*      | O*      | 0       |            | 0       |

| Nd    | 0       | 0       | 0       | 0       | 0       | 0    | 0       | 0     | 0     | 0       | 0       | 0       | 0~31       | 0       |

- When move control "EN" = 1 or "EN↑" (**P** instruction) changes from 0 to 1, will move the bit status specified by Ns within S into the bit specified by Nd within D.

- When the operand is 16 bit, the effective range of N is 0~15. For 32 bit (☐ instruction) operand the effective range is 0~31. N beyond this range will set the N value error flag "ERR" to 1, and do not carry out this instruction.

The instruction at left moves the status of B11 (X11) within S into the B7 position within D. Except bit B7, other bits within D does not change.

| FUN 43 DP NIBBLE MOVE | FUN 43 DP<br>NBMV |

|-----------------------|-------------------|

|-----------------------|-------------------|

Move control -EN↑

S:

Ns:

D:

Nd:

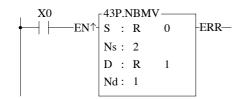

S: Source data to be moved

Ns: Assign Ns nibble within S as source nibble

D: Destination register to be moved

Nd: Assign Nd nibble within D as target nibble

S, Ns, D, Nd may combine with V, Z to serve indirect address application

| Range | WX         | WY    | WM     | WS    | TMR     | CTR  | HR      | IR      | OR    | SR       | ROR   | DR    | K         | XR      |

|-------|------------|-------|--------|-------|---------|------|---------|---------|-------|----------|-------|-------|-----------|---------|

|       | WX0        | WY0   | WM0    | WS0   | T0      | C0   | R0      | R3840   | R3904 | R3968    | R5000 | D0    | 16/32-bit | V       |

| Ope-  |            |       |        |       |         |      |         |         |       |          |       |       | +/-       | ` `     |

| rand  | WX240      | WY240 | WM1896 | WS984 | T255    | C255 | R3839   | R3903   | R3967 | R4167    | R8071 | D3071 | number    | Z       |

| S     | $\bigcirc$ |       | 0      | 0     | $\circ$ | 0    | $\circ$ | $\circ$ | 0     | 0        | 0     | 0     | 0         | $\circ$ |

| Ns    | 0          | 0     | 0      | 0     | 0       | 0    | 0       | 0       | 0     | 0        | 0     | 0     | 0~7       | $\circ$ |

| D     |            |       | 0      | 0     | $\circ$ | 0    | $\circ$ |         | 0     | <b>*</b> | O*    | 0     |           | $\circ$ |

| Nd    | 0          | 0     | 0      | 0     | $\circ$ | 0    | 0       | 0       | 0     | 0        | 0     | 0     | 0~7       | 0       |

- When move control "EN" = 1 or "EN↑" (☐ instruction) has a transition from 0 to 1, will move the Ns'th nibble from within S to the nibble specified by Nd within D. (A nibble is comprised by 4 bits. Starting from the lowest bit of the register, B0, each successive 4 bits form a nibble, so B0~B3 form nibble 0, B4~B7 form nibble 1, etc...)

- When the operand is 16 bit, the effective range of Ns or Nd is 0~3. For 32 bit ( instruction) operand the range is 0~7. Beyond this range, will set the N value error flag "ERR" to 1, and do not carry out this instruction.

The instruction at left moves the third nibble NB2 (B8~B11) within S to the first nibble NB1 (B4~B7) within D. Other nibbles within D remain unchanged.

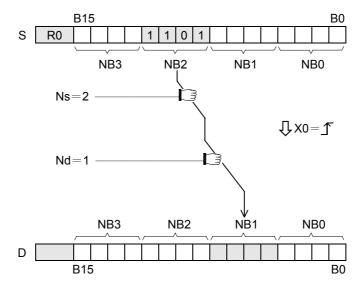

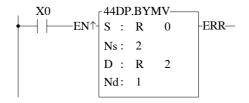

FUN 44 DP BYMV BYMV FUN 44 DP BYMV

S : Source data to be moved

Ns: Assign Ns byte within S as source byte

D : Destination register to be moved

Nd: Assign Nd byte within D as target byte

S, Ns, D, Nd may combine with V, Z to serve indirect address application

| Range | WX      | WY         | WM     | WS    | TMR     | CTR     | HR      | IR      | OR      | SR        | ROR       | DR      | K          | XR      |

|-------|---------|------------|--------|-------|---------|---------|---------|---------|---------|-----------|-----------|---------|------------|---------|

|       | WX0     | WY0        | WM0    | WS0   | T0      | C0      | R0      | R3840   | R3904   | R3968     | R5000     | D0      | 16/32-bit  | V       |

| Ope-  |         | - 1        |        |       |         |         |         |         |         |           |           |         | +/- number | `       |

| rand  | WX240   | WY240      | WM1896 | WS984 | T255    | C255    | R3839   | R3903   | R3967   | R4167     | R8071     | D3071   |            | Z       |

| S     | $\circ$ | $\bigcirc$ | 0      |       | $\circ$ | 0       | 0       | $\circ$ | $\circ$ | $\circ$   | $\circ$   | $\circ$ | 0          | $\circ$ |

| Ns    | $\circ$ | $\bigcirc$ | 0      |       | $\circ$ | 0       | 0       | $\circ$ | $\circ$ | $\circ$   | $\circ$   | $\circ$ | 0~3        | $\circ$ |

| D     |         | $\bigcirc$ | 0      |       | $\circ$ | $\circ$ | $\circ$ |         | $\circ$ | <b>O*</b> | <b>O*</b> | $\circ$ |            | $\circ$ |

| Nd    | 0       | 0          | 0      | 0     | 0       | 0       | 0       | 0       | 0       | 0         | 0         | 0       | 0~3        | $\circ$ |

- When move control "EN" = 1 or "EN ↑" ( instruction) has a transition from 0 to 1, move Nsth byte within S to Ndth byte position within D. (A byte is comprised of 8 bits. Starting from the lowest bit of the register, B0, each successive eight bits form a byte, so B0~B7 form byte 0, B8~B15 form byte 1, etc...)

- When the operand is 16 bit, the effective range of Ns or Nd is 0~1. For 32 bit (☐ instruction) operand, the range is 0~3. Beyond this range, will set the N value error flag "ERR" to 1, and do not carry out this instruction.

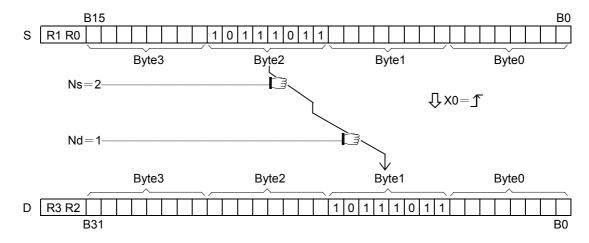

The instruction at left moves the third byte (B16~B23) within S (32 bit register composed of R1R0), to the first byte within D (32 bit register composed of R3R2). Other bytes within D remain unchanged.

#### Data movement instructions

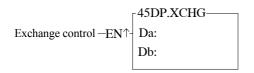

Da : Register a to be exchanged

Db: Register b to be exchanged

Da, Db may combine with  $V,\,Z$  to serve indirect address application

| Range | WY    | WM     | WS    | TMR  | CTR  | HR    | OR    | SR    | ROR   | DR    | XR |

|-------|-------|--------|-------|------|------|-------|-------|-------|-------|-------|----|

|       | WY0   | WM0    | WS0   | T0   | C0   | R0    | R3904 | R3968 | R5000 | D0    | ٧  |

| Ope-  |       |        |       |      |      |       |       |       |       |       | `  |

|       |       |        |       |      |      |       |       |       |       |       |    |

|       | WY240 | WM1896 | WS984 | T255 | C255 | R3839 | R3967 | R4167 | R8071 | D3071 | Z  |

|       | WY240 | WM1896 | WS984 | T255 | C255 | R3839 | R3967 | R4167 | R8071 | D3071 | Z  |

• When exchange control "EN" = 1 or "EN↑" (☐ instruction) has a transition from 0 to 1, will exchanges the contents of register Da and register Db in 16 bits or 32 bits (☐ instruction) format.

• The instruction at left exchanges the contents of the 16-bit R0 and R1 registers.

|    | E  | 315 | , |   |   |   |   |   |   |   |   |   |   |   |   |   | B0 |

|----|----|-----|---|---|---|---|---|---|---|---|---|---|---|---|---|---|----|

| Da | R0 | 0   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0  |

| Db | R1 | 1   | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1  |

$$\int X0 = \int$$

|    | E  | 315 | ) |   |   |   |   |   |   |   |   |   |   |   |   |   | B0_ |

|----|----|-----|---|---|---|---|---|---|---|---|---|---|---|---|---|---|-----|

| Da | R0 | 1   | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1   |

| Db | R1 | 0   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0   |

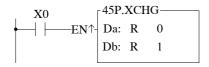

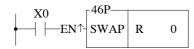

FUN 46 P SWAP

BYTE SWAP

FUN 46 P

SWAP

D : Register for byte data swap

D may combine with V, Z to serve indirect address application

| Range | WY    | WM     | WS    | TMR  | CTR  | HR    | OR    | SR    | ROR   | DR    | XR  |

|-------|-------|--------|-------|------|------|-------|-------|-------|-------|-------|-----|

|       | WY0   | WM0    | WS0   | T0   | C0   | R0    | R3904 | R3968 | R5000 | D0    | V   |

| Ope-  |       |        |       |      |      |       |       |       |       |       | ` ` |

| rand  | WY240 | WM1896 | WS984 | T255 | C255 | R3839 | R3967 | R4167 | R8071 | D3071 | Z   |

| D     | 0     | 0      | 0     | 0    | 0    | 0     | 0     | O*    | O*    | 0     | 0   |

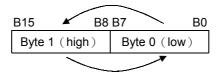

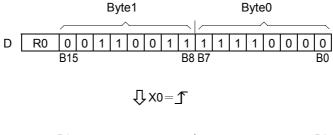

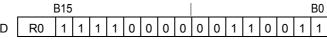

• When swap control "EN" = 1 or "EN ↑" ( instruction) has a transition from 0 to 1, swap the data of the low byte, Byte 0 (B0~B7), and the high byte, Byte 1 (B8~B15), in the 16 bit register specified by D.

● The instruction at left swaps the data of the low byte (B0~B7) and the high byte (B8~B15) in R0. The results are as follows:

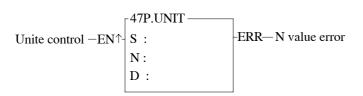

S: Starting source register to be united

N: Number of nibbles to be united

D: Registers storing united data

S, N, D may combine with V, Z to serve indirect address application

| Range | WX    | WY    | WM     | WS    | TMR     | CTR     | HR      | IR      | OR    | SR      | ROR       | DR      | K          | XR      |

|-------|-------|-------|--------|-------|---------|---------|---------|---------|-------|---------|-----------|---------|------------|---------|

|       | WX0   | WY0   | WM0    | WS0   | T0      | C0      | R0      | R3840   | R3904 | R3968   | R5000     | D0      | 1          | V       |

| Ope-\ |       |       |        |       |         |         |         |         |       |         |           |         |            | `       |

| rand  | WX240 | WY240 | WM1896 | WS984 | T255    | C255    | R3839   | R3903   | R3967 | R4167   | R8071     | D3071   | 4          | Ζ       |

| S     | 0     | 0     | 0      | 0     | 0       | 0       | 0       | 0       | 0     | 0       | 0         | 0       |            | $\circ$ |

| N     | 0     | 0     | 0      | 0     | $\circ$ | $\circ$ | $\circ$ | $\circ$ | 0     | $\circ$ | 0         | $\circ$ | $\bigcirc$ | $\circ$ |

| D     |       | 0     | 0      | 0     | 0       | 0       | 0       |         | 0     | O*      | <b>O*</b> | 0       |            | 0       |

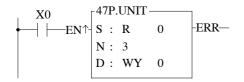

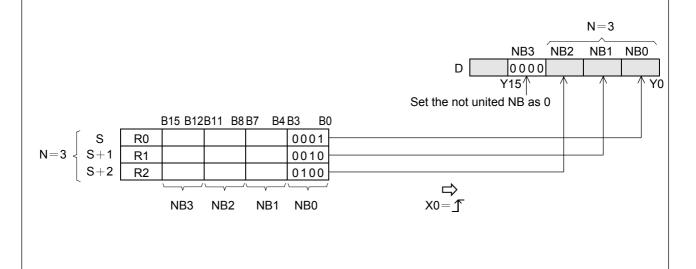

- When unite control "EN" = 1 or "EN↑" (☐ instruction) has a transition from 0 to 1, take out the lowest nibbles NB0, of N successive registers starting from S, and fill them into NB0, NB1, .....NBn-1 of D in ascending order. Nibbles not yet filled in D (when N is odd) are filled with 0. (A nibble is comprised by 4 bits. Starting from the lowest bit in the register, B0, each successive four bits form a nibble, so B0~B3 form nibble 0, B4~B7 form nibble 1, etc...).

- This instruction only provides WORD (16 bit) operand. Because of this, there are usually only 4 nibbles can be involved. Therefore the effective range of N is 1~4. Beyond this range, will set the N value error flag "ERR" to 1, and do not carry out this instruction.

The instruction at left takes out NB0 from 3 registers, R0, R1 and R2, and fills them into NB0~NB2 within WY0 register.

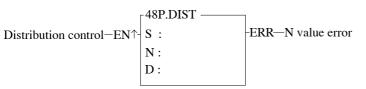

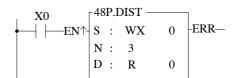

FUN 48 P NIBBLE DISTRIBUTE

FUN 48 D DIST

S: Source data to be distributed

N: Number of nibbles to be distributed

D: Starting register storing distribution data

S, N, D may combine with V, Z to serve indirect address application

| Range | WX    | WY    | WM     | WS    | TMR  | CTR  | HR    | IR    | OR    | SR        | ROR   | DR    | K      | XR |

|-------|-------|-------|--------|-------|------|------|-------|-------|-------|-----------|-------|-------|--------|----|

|       | WX0   | WY0   | WM0    | WS0   | T0   | C0   | R0    | R3840 | R3904 | R3968     | R5000 | D0    | 16-bit | V  |

| Ope-  |       |       |        |       |      |      |       |       |       |           |       |       | +/-    | `  |

| rand  | WX240 | WY240 | WM1896 | WS984 | T255 | C255 | R3839 | R3903 | R3967 | R4167     | R8071 | D3071 | number | Z  |

| S     | 0     | 0     | 0      | 0     | 0    | 0    | 0     | 0     | 0     | 0         | 0     | 0     | 0      | 0  |

| N     | 0     | 0     | 0      | 0     | 0    | 0    | 0     | 0     | 0     | 0         | 0     | 0     | 1~4    | 0  |

| D     |       | 0     | 0      | 0     | 0    | 0    | 0     |       | 0     | <b>O*</b> | O*    | 0     |        | 0  |

- When distribution control "EN" = 1 or "EN↑" ( instruction) has a transition from 0 to 1, will take N successive nibbles starting from the lowest nibble NB0 within S, and distribute them in ascending order into the 0 nibbles of N registers starting from D. The nibbles other than NB0 in each of the registers within D are all set to zero. (A nibble is comprised by 4 bits. Starting from the lowest bit in a register, B0, each successive 4 bits form a nibble, so B0~B3 form nibble 0, B4~B7 form nibble 1, etc...)

- This instruction only provides WORD (16 bit) operand. Therefore there are usually only 4 nibbles can be involved, so the effective value of N is 1~4. Beyond this range, will set the N value error flag "ERR" to 1, and do not carry out this instruction.

The instruction at left writes NB0~NB2 from the WX0 register into the NB0 of the 3 consecutive registers R0~R2.

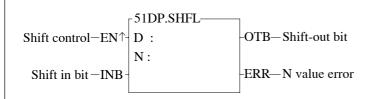

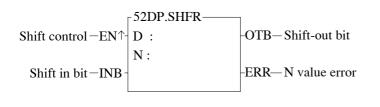

D : Register to be shifted

N: Number of bits to be shifted

N, D may combine with V, Z to serve indirect address application

| Range | WX    | WY    | WM     | WS    | TMR     | CTR  | HR      | IR    | OR      | SR       | ROR      | DR      | K     | XR      |

|-------|-------|-------|--------|-------|---------|------|---------|-------|---------|----------|----------|---------|-------|---------|

|       | WX0   | WY0   | WM0    | WS0   | T0      | C0   | R0      | R3840 | R3904   | R3968    | R5000    | D0      | 1 1   | V       |

| Ope-  |       |       |        |       |         |      |         |       |         |          |          |         | or    | •       |

| rand  | WX240 | WY240 | WM1896 | WS984 | T255    | C255 | R3839   | R3903 | R3967   | R4167    | R8071    | D3071   | 16 32 | Z       |

| D     |       | 0     | 0      | 0     | $\circ$ | 0    | $\circ$ |       | $\circ$ | <b>*</b> | <b>*</b> | $\circ$ |       | $\circ$ |

| N     | 0     | 0     | 0      | 0     | 0       | 0    | 0       | 0     | 0       | 0        | 0        | 0       | 0     | $\circ$ |

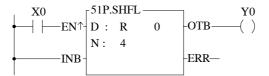

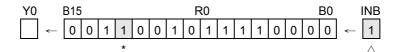

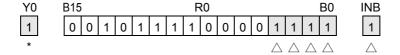

- When shift control "EN" = 1 or "EN↑" ( instruction) has a transition from 0 to 1, will shift the data of the D register towards the left by N successive bits (in ascending order). After the lowest bit B0 has been shifted left, its position will be replaced by shift-in bit INB, while the status of shift-out bits B15 or B31 ( instruction) will appear at shift-out bit "OTB".

- If the operand is 16 bit, the effective range of N is 1~16. For 32 bits (**D** instruction) operand, it is 1~32. Beyond this range, will set the N value error flag "ERR" to 1, and do not carry out this instruction.

The instruction at left shifts the data in register R0 towards the left by 4 successive bits. The results are shown below.

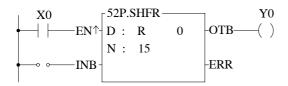

D : Register to be shifted

N : Number of bits to be shifted

D, N may combine with V, Z to serve indirect address application

| R            | ange | WX    | WY    | WM     | WS      | TMR     | CTR     | HR    | IR    | OR      | SR       | ROR   | DR      | K     | XR      |

|--------------|------|-------|-------|--------|---------|---------|---------|-------|-------|---------|----------|-------|---------|-------|---------|

|              |      | WX0   | WY0   | WM0    | WS0     | T0      | C0      | R0    | R3840 | R3904   | R3968    | R5000 | D0      | 1 1   | V       |

| Ope-<br>rand |      |       |       |        |         |         |         |       |       |         |          |       |         | or    | `       |

| rand         |      | WX240 | WY240 | WM1896 | WS984   | T255    | C255    | R3839 | R3903 | R3967   | R4167    | R8071 | D3071   | 16 32 | Z       |

| D            | )    |       | 0     | 0      | $\circ$ | $\circ$ | $\circ$ | 0     |       | $\circ$ | <b>*</b> | O*    | $\circ$ |       | $\circ$ |

| N            | 1    | 0     | 0     | 0      | 0       | 0       | 0       | 0     | 0     | 0       | 0        | 0     | 0       | 0     | 0       |

- When shift control "EN" = 1 or "EN↑" (☐ instruction) has a transition from 0 to 1, will shift the data of D register towards the right by N successive bits (in descending order). After the highest bits, B15 or B31 (☐ instruction) have been shifted right, their positions will be replaced by the shift-in bit INB, while shift-out bit B0 will appear at shift-out bit "OTB".

- If the operand is 16 bit, the effective range of N is 1~16. For 32 bits (**D** instruction) operand, it is 1~32. Beyond this range, will set the N value error flag "ERR" to 1, and do not carry out this instruction.

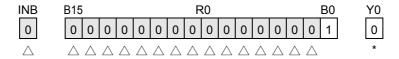

The instruction at left shifts the data in R0 register towards the right by 15 successive bits. The results are shown below.

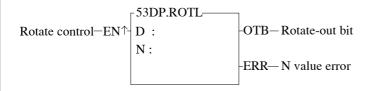

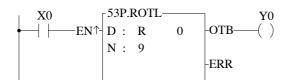

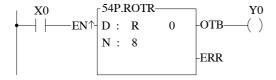

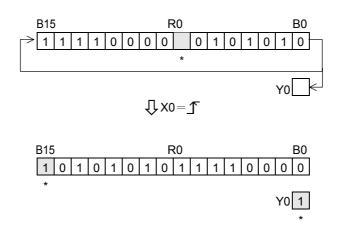

D : Register to be rotated

N : Number of bits to be rotated

D, N may combine with V, Z to serve indirect address application

| Rang | je WX | WY    | WM     | WS    | TMR  | CTR     | HR    | IR    | OR    | SR        | ROR       | DR    | K     | XR  |

|------|-------|-------|--------|-------|------|---------|-------|-------|-------|-----------|-----------|-------|-------|-----|

|      | WX0   | WY0   | WM0    | WS0   | T0   | C0      | R0    | R3840 | R3904 | R3968     | R5000     | D0    | 1 1   | ٧   |

| Ope- | 1     |       |        |       |      |         |       |       |       |           |           |       | or    | ` ` |

| rand | WX240 | WY240 | WM1896 | WS984 | T255 | C255    | R3839 | R3903 | R3967 | R4167     | R8071     | D3071 | 16 32 | Z   |

| D    |       | 0     | 0      | 0     | 0    | $\circ$ | 0     |       | 0     | <b>O*</b> | <b>O*</b> | 0     |       | 0   |

| N    | 0     | 0     | 0      | 0     | 0    | 0       | 0     | 0     | 0     | 0         | 0         | 0     | 0     | 0   |

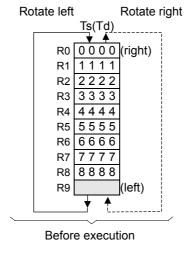

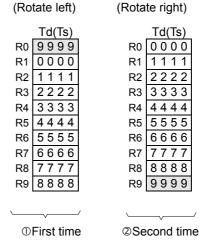

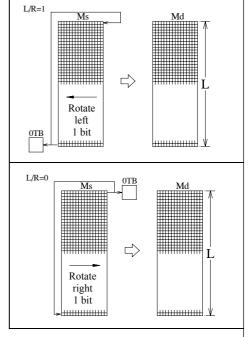

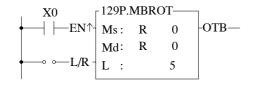

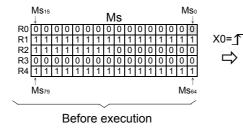

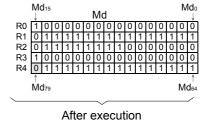

- When rotate control "EN" = 1 or "EN↑" ( instruction) has a transition from 0 to 1, will rotate the data of D register towards the left by N successive bits (in ascending order, ie. in a 16-bit instruction, B0→B1, B1→B2, ...., B30→B31, B31→B0). At the same time, the status of the rotated out bits B15 or B31 ( instruction) will appear at rotate-out bit "OTB".

- If the operand is 16 bit, the effective range of N is 1~16. For 32 bits (**D** instruction) operand, it is 1~32. Beyond this range, will set the N value error flag "ERR" to 1, and do not carry out this instruction.

The instruction at left rotates data from the R0 register towards the left 9 successive bits. The results are shown below.

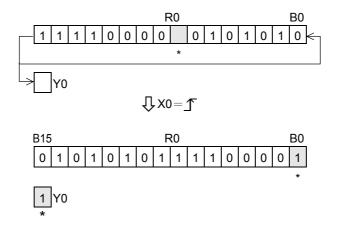

D : Register to be rotated

N: Number of bits to be rotated

D, N may combine with V, Z to serve indirect address application

| Range | WX    | WY      | WM     | WS    | TMR     | CTR  | HR      | IR    | OR      | SR       | ROR       | DR      | K     | XR      |

|-------|-------|---------|--------|-------|---------|------|---------|-------|---------|----------|-----------|---------|-------|---------|

|       | WX0   | WY0     | WM0    | WS0   | T0      | C0   | R0      | R3840 | R3904   | R3968    | R5000     | D0      | 1 1   | V       |

| Ope-  |       |         |        |       |         |      |         |       |         |          |           |         | or    | `       |

| rand  | WX240 | WY240   | WM1896 | WS984 | T255    | C255 | R3839   | R3903 | R3967   | R4167    | R8071     | D3071   | 16 32 | Z       |

| D     |       | $\circ$ | 0      | 0     | $\circ$ | 0    | $\circ$ |       | $\circ$ | <b>*</b> | <b>O*</b> | $\circ$ |       | $\circ$ |

| N     | 0     | 0       | 0      | 0     | 0       | 0    | 0       | 0     | 0       | 0        | 0         | 0       | 0     | 0       |

- When rotate control "EN" = 1 or "EN↑" (☐ instruction) has a transition from 0 to 1, will rotate the bit data of D register towards the right by N successive bits (in descending order, ie. in a 16-bit instruction, B15→B14, B14→B13, ...., B1→B0, B0→B15. In a 32-bit instruction, B31→B30, B30→B29, ...., B1→B0, B0→B31). At the same time, the status of the rotated out B0 bits will appear at the rotate-out bit "OTB".

- If the operand is 16 bit, the effective range of N is 1~16. For 32 bits ( instruction) operand, it is 1~32. Beyond this range, will set the N value error flag "ERR" to 1, and do not carry out this instruction.

The instruction at left rotates data from R0 register towards the right 8 successive bits. The results are shown below.

| FUN 57 P<br>DECOD | DECODE | FUN 57 PDECOD |

|-------------------|--------|---------------|

|                   | DECODE |               |

Decode control  $-EN^{\uparrow}$  S: -ERR—Range error  $N_S:$   $N_L:$  D:

S : Source data register to be decoded (16 bits)

$\ensuremath{N_{\text{S}}}$  : Starting bits to be decoded within S

N<sub>L</sub>: Length of decoded value (1~8 bits)D: Starting register storing decoded results

(2~256 points = 1~16 words)

$S, N_S, N_{L_{,}} D$  may combine with V, Z to serve indirect address application

| Range          | WX    | WY      | WM     | WS      | TMR      | CTR    | HR    | IR      | OR      | SR       | ROR       | DR      | К                    | XR      |

|----------------|-------|---------|--------|---------|----------|--------|-------|---------|---------|----------|-----------|---------|----------------------|---------|

| Ope-<br>rand   | WX0   | WY0     | WM0    | WS0     | T0<br> - | C0<br> | R0    | R3840   | R3904   | R3968    | R5000     | D0<br>  | 16-bit<br>+/- number | V<br>,  |

| rand           | WX240 | WY240   | WM1896 | WS984   | T255     | C255   | R3839 | R3903   | R3967   | R4167    | R8071     | D3071   | ·/ Humber            | Ζ       |

| S              | 0     | 0       | 0      | 0       | 0        | 0      | 0     | 0       | 0       | 0        | 0         | 0       | 0                    | $\circ$ |

| N <sub>S</sub> | 0     | $\circ$ | 0      | 0       | $\circ$  | 0      | 0     | $\circ$ | $\circ$ | $\circ$  | 0         | $\circ$ | 0~15                 | $\circ$ |

| $N_L$          | 0     | $\circ$ | 0      | 0       | $\circ$  | 0      | 0     | $\circ$ | $\circ$ | $\circ$  | 0         | $\circ$ | 1~8                  | $\circ$ |

| D              |       | $\circ$ | 0      | $\circ$ | $\circ$  | 0      | 0     |         | $\circ$ | <b>*</b> | <b>O*</b> | $\circ$ |                      | $\circ$ |

- This instruction, will set a single bit among the total of 2<sup>NL</sup> discrete points (D) to 1 and the others bit are set to 0. The bit number to be set to 1 is specified by the value comprised by BN<sub>S</sub>∼BN<sub>S</sub>+N<sub>L</sub>−1 of S (which is called the decode value, BN<sub>S</sub> is the starting bit of the decode value, and BN<sub>S</sub>+N<sub>L</sub>−1 is the end value) ,.

- When decode control "EN" = 1 or "EN ↑" ( $\blacksquare$  instruction) has a transition from 0 to 1, will take out the value BN<sub>S</sub>~BN<sub>S</sub>+N<sub>L</sub>-1 from S. And with this value to locate the bit position and set D accordingly, and set all the other bit to zero

- This instruction only provides 16 bit operand, which means S only has B0~B15. Therefore the effective range of Ns is 0~15, and the N<sub>L</sub> length of the decode value is limited to 1~8 bits. Therefore the width of the decoded result D is 2<sup>1~8</sup> points = 2~256 points = 1~16 words (if 16 points are not sufficient, 1 word is still occupied). If the value of N<sub>S</sub> or N<sub>L</sub> is beyond the above range, will set the range-error flag "ERR" to 1, and do not carry out this instruction.

- If the end bit value exceeds the B15 of S, then will extend toward B0 of S + 1. However if this occurs then S+1 can't exceed the range of specific type of operand (ie. If S is of D type register then S+1 can't be D3072). If violate this, then this instruction only takes out the bits from starting bit BNs to its highest limit as the decode value.

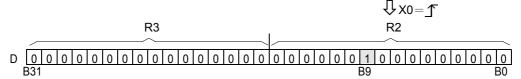

The instruction at left takes out the data of five successive bits from X3 to X7 within the WX0 register and decodes it. The results are then stored in the 32-bit register starting at R2.

Length of decode value N<sub>L</sub>=5,so bit value is formed by X7~X3 (equal 9)

Because  $N_L$ =5,the width of D is  $2^5$ = 32 point = 2 word. That is, D is formed by R3R2, and the decoded value is 01001=9, therefore B9 (the 10th point) within D is set to 1, and all other points are 0.

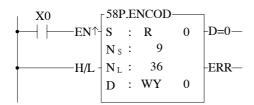

FUN 58 PENCODE ENCODE ENCOD

Encode control—EN↑ S: D=0—All is 0  $N_S: D: D=0$  ERR—Range error D: D: D=0

S : Starting register to be encoded

N<sub>S</sub>: Bit position within S as the encoding start point

N<sub>L</sub>: Number of encoding discrete points (2~256)

D : Number of register storing encoding results (1 word)

$S,\,N_S,\,N_L,\,D$  may combine with  $V,\,Z$  to serve indirect address application

| Range          | WX        | WY        | WM         | WS        | TMR      | CTR      | HR        | IR    | OR        | SR        | ROR       | DR        | K             | XR      |

|----------------|-----------|-----------|------------|-----------|----------|----------|-----------|-------|-----------|-----------|-----------|-----------|---------------|---------|

|                | WX0       | WY0       | WM0        | WS0       | T0       | C0       | R0        | R3840 | R3904     | R3968     | R5000     | D0        | 16-bit        | V       |

| Ope-<br>rand   | <br>WX240 | <br>WY240 | <br>WM1896 | <br>WS984 | <br>T255 | <br>C255 | <br>R3839 | R3903 | <br>R3967 | <br>R4167 | <br>R8071 | <br>D3071 | +/-<br>number | Z       |

| S              | 0         | 0         | 0          | 0         | 0        | 0        | 0         | 0     | 0         | 0         | 0         | 0         |               | 0       |

| Ns             | 0         | 0         | 0          | 0         | 0        | 0        | 0         | 0     | 0         | 0         | 0         | 0         | 0~15          | $\circ$ |

| N <sub>L</sub> |           | 0         | 0          | 0         | 0        | 0        | 0         |       | 0         | 0         | 0         | 0         | 2~256         |         |

| D              |           | 0         | 0          | 0         | 0        | 0        | 0         |       | 0         | O*        | O*        | 0         |               |         |

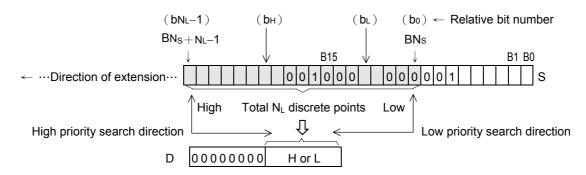

When encode control "EN" = 1 or "EN↑" (☐ instruction) has a transition from 0 to 1, will starting from the points specified by Ns within S, take out towards the left (high position direction) N<sub>L</sub> number of successive bits BN<sub>S</sub>~BN<sub>S</sub>+N<sub>L</sub>-1 (BN<sub>S</sub> is called the encoding start point, and its relative bit number is b0;BN<sub>S</sub>+N<sub>L</sub>-1 is called the encoding end point, and its relative bit number is BN<sub>L</sub>-1). From left to right do higher priority (when H/L=1) encoding or from right to left do lower priority (when H/L=0) encoding (i.e. seek the first bit with the value of 1, and the relative bit number of this point will be stored into the low byte (B0~B7) of encoded resultant register D, and the high byte of D will be filled with 0.

- ◆ As shown in the diagram above, for high priority encoding, the bit first to find is b<sub>H</sub> (with a value of 12), and for low priority encoding, the bit first to find b<sub>L</sub> (with a value of 4). Among the N<sub>L</sub> discrete points there must be at least one bit with value of 1. If all bits are 0, will not to carry out this instruction, and the all zero flag "D=0" will set to 1.

- Because S is a 16-bit register, Ns can be 0~15, and is used to assign a point of B0~B15 within S as the encoding start point (b0). The value of N<sub>L</sub> can be 2~256, and it is used to identify the encoding end point, i.e. it assigns N<sub>L</sub> successive single points starting from the start point (b0) towards the left (high position direction) as the encoding zone (i.e. b0~bN<sub>L</sub>−1). If the value of Ns or N<sub>L</sub> exceeds the above value, then do not carry out this instruction, and set the range-error flag "ERR" as 1.

#### Code conversion instructions

● If the encoding end point (bNL-1) beyond the B15 of S, then continue extending towards S+1, S+2, but it must not exceed the range of specific type of operand. If it goes beyond this, then this instruction can only take the discrete points between b0 and the highest limit into account for encoding.

• The instruction at left is a high priority encode example. When X0 goes from 0 to 1, will take out toward left 36 successive bits starting from B9 (b0) specified by Ns within S, and perform high priority encoding (because H/L = 1). That is, starting from b35 (encoding end point), move right to find the first bit with the value of 1. The resultant value of this example is b26, so the value of D is 001AH=26, as shown in the diagram below.

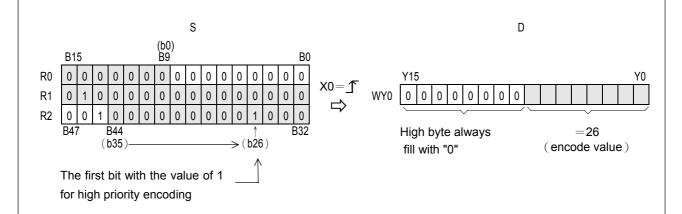

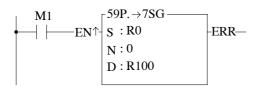

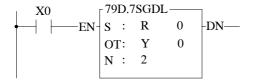

| FUN 59 <b>₽</b><br>→7SG | 7-SEGMENT CONVERSION | FUN 59 <b>P</b><br>→7SG |

|-------------------------|----------------------|-------------------------|

|-------------------------|----------------------|-------------------------|

S: Source data to be converted

N: The nibble number within S for conversion

|    | Range | WX      | WY    | WM      | WS      | TMR     | CTR     | HR      | IR    | OR      | SR    | ROR   | DR      | K       | XR      |

|----|-------|---------|-------|---------|---------|---------|---------|---------|-------|---------|-------|-------|---------|---------|---------|

|    |       | WX0     | WY0   | WM0     | WS0     | T0      | C0      | R0      | R3840 | R3904   | R3968 | R5000 | D0      | 16-bit  | V       |

|    | pe-   |         |       |         |         |         |         |         |       |         |       |       |         | +/-     | ` `     |

| ra | nd    | WX240   | WY240 | WM1896  | WS984   | T255    | C255    | R3839   | R3903 | R3967   | R4167 | R8071 | D3071   | number  | Z       |

|    | S     | $\circ$ | 0     | $\circ$ | $\circ$ | $\circ$ | $\circ$ | $\circ$ | 0     | $\circ$ | 0     | 0     | $\circ$ | $\circ$ | $\circ$ |

|    | Ν     | 0       | 0     | 0       | 0       | $\circ$ | $\circ$ | 0       | 0     | 0       | 0     | 0     | 0       | 0~3     | $\circ$ |

|    | D     |         | 0     | 0       | 0       | 0       | 0       | 0       |       | 0       | O*    | O*    | 0       |         | 0       |

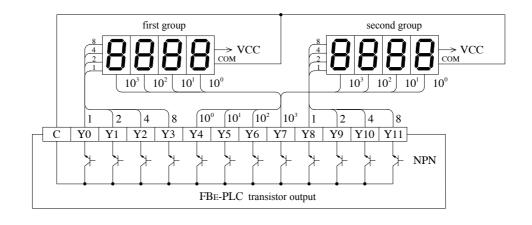

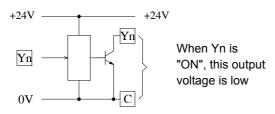

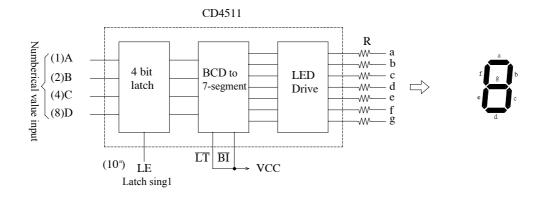

- When conversion control "EN" = 1 or "EN↑" (☐ instruction) has a transition from 0 to 1, will convert N+1 number of nibbles (A nibble is comprised by 4 successive bits, so B0~B3 of S form nibble 0, B4~B7 form nibble 1, etc...) within S to 7-segment code, and store the code into a low byte of D (High bytes does not change). The 7 segment within D are put in sequence, with "a" segment placed at B6, "b" segment at B5, ...., "g" segment at B0. B7 is not used and is fixed as 0. For details please refer the "7-segment code and display pattern table" shown in page 9-31.

- Because this instruction is limited to 16 bits, and S only has 4 nibbles (NB0~NB3), the effective range of N is 0~3. Beyond this range, will set the N value flag error "ERR" to 1, and does not carry out this instruction.

- Care should be taken on total nibbles to be converted is N+1. N=0 means one digit to convert, N=1 means two digits to convert etc...

- When using the FATEK 7-segment expansion module(FB-7SG) and the FUN84 (7SEG0) handy instruction for mixing decoding and non-decoding application, FUN59 and FUN84 can be combined to simplify the program design.(Please refer the example in chapter 17)

#### Code conversion instructions

R0=0001H

FUN 59 **P** →7SG

#### 7-SEGMENT CONVERSION

FUN 59 **₽** →7SG

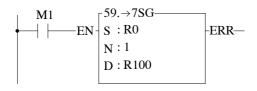

⟨ Example 1 ⟩ When M1 OFF→ON, convert hexadecimal to 7-Segment

Figure left shown the conversion of first digit(nibble) of R0 to 7-segment and store in low byte of R100, the high byte of R100 remain unchanged.

Original R100=0000H

**→**

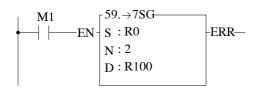

〈Example 2〉 When M1 ON, convert the hexadecimal to 7-Segment

R100=0030H(1)

- Instruction at left will convert the first and the second digit of R0 to 7-segment and store in R100.

- The low byte of R100 stores first digit.

- The high byte of R100 stores second digit.

R0=0056H → R100=5B5FH (56)

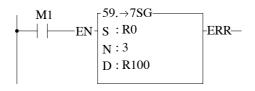

〈Example 3〉 When M1 ON, converting hexadecimal to 7-Segment

- Instruction at left will convert the first, second and third digit of R0 to 7-segment and store in R100 and R101.

- The low byte of R100 stores first digit.

- The high byte of R100 stores second digit.

- The low byte of R101 stores third digit.

- The high byte of R10 remain unchanged.

Original R101=0000H

R0=0A48H → R100=337FH (48)

R101=0077H (A)

〈 Example 4 〉 When M1 ON, convert hexadecimal to 7-Segment

- Instruction at left will convert 1~4 digit of R0 to 7-segment and store in R100 and R101.

- The low byte of R100 stores first digit.

- The high byte of R100 stores second digit.

- The low byte of R101 stores third digit.

- The high byte of R10 stores 4<sup>th</sup> digit.

R0=2790H → R100=7B7EH (90) R101=6D72H (27) FUN 59 **P** →7SG

#### 7-SEGMENT CONVERSION

FUN 59 ₽ →7SG

| Nibble da          | ata of S         | 7 aggment                   |         |         | l       | _ow by  | rte of C | )       |         |         | - Display |  |

|--------------------|------------------|-----------------------------|---------|---------|---------|---------|----------|---------|---------|---------|-----------|--|

| Hexadecimal number | Binary<br>number | 7-segment<br>display format | B7<br>• | B6<br>a | B5<br>b | B4<br>c | B3<br>d  | B2<br>e | B1<br>f | B0<br>g | pattern   |  |

| 0                  | 0000             |                             | 0       | 1       | 1       | 1       | 1        | 1       | 1       | 0       |           |  |

| 1                  | 0001             |                             | 0       | 0       | 1       | 1       | 0        | 0       | 0       | 0       | 0         |  |

| 2                  | 0010             |                             | 0       | 1       | 1       | 0       | 1        | 1       | 0       | 1       |           |  |

| 3                  | 0011             |                             | 0       | 1       | 1       | 1       | 1        | 0       | 0       | 1       |           |  |

| 4                  | 0100             | B6 a                        | 0       | 0       | 1       | 1       | 0        | 0       | 1       | 1       | 4         |  |

| 5                  | 0101             | B1 f b B5                   | 0       | 1       | 0       | 1       | 1        | 0       | 1       | 1       | 5         |  |

| 6                  | 0110             | B2 e c B4                   | 0       | 1       | 0       | 1       | 1        | 1       | 1       | 1       | 6         |  |

| 7                  | 0111             | В3                          | 0       | 1       | 1       | 1       | 0        | 0       | 1       | 0       |           |  |

| 8                  | 1000             |                             | 0       | 1       | 1       | 1       | 1        | 1       | 1       | 1       | 8         |  |

| 9                  | 1001             |                             | 0       | 1       | 1       | 1       | 1        | 0       | 1       | 1       | 9         |  |

| А                  | 1010             |                             | 0       | 1       | 1       | 1       | 0        | 1       | 1       | 1       | A         |  |

| В                  | 1011             |                             | 0       | 0       | 0       | 1       | 1        | 1       | 1       | 1       |           |  |

| С                  | 1100             |                             | 0       | 1       | 0       | 0       | 1        | 1       | 1       | 0       |           |  |

| D                  | 1101             |                             | 0       | 0       | 1       | 1       | 1        | 1       | 0       | 1       | d         |  |

| E                  | 1110             |                             | 0       | 1       | 0       | 0       | 1        | 1       | 1       | 1       |           |  |

| F                  | 1111             |                             | 0       | 1       | 0       | 0       | 0        | 1       | 1       | 1       | F         |  |

7-segment display pattern table

#### Code conversion instructions

FUN 60

→ ASC

ASCII CONVERSION

FUN 60

→ ASC

$\begin{array}{c} \text{Conversion control-EN} \\ \hline \\ S : \triangle \triangle \triangle \triangle \triangle \triangle \triangle \\ \\ D : \end{array}$

S: Alphanumerics to be converted into ASCII code

D: Starting register storing ASCII results

| Range        | WY                       | WM                        | WS                | TMR                    | CTR             | HR               | OR                  | SR                  | ROR                 | DR               | Alphanumeric         |

|--------------|--------------------------|---------------------------|-------------------|------------------------|-----------------|------------------|---------------------|---------------------|---------------------|------------------|----------------------|

| Ope-<br>rand | WY0<br> <br> <br>  WY240 | WM0<br> <br> <br>  WM1896 | WS0<br> <br>WS984 | T0<br> <br> <br>  T255 | C0<br>-<br>C255 | R0<br> <br>R3839 | R3904<br> <br>R3967 | R3968<br> <br>R4167 | R5000<br> <br>R8071 | D0<br> <br>D3071 | 1∼12<br>alphanumeric |

|              | VV 12+0                  | VVIVI 1050                |                   |                        | -               |                  |                     |                     |                     | -                |                      |

| S            | VV1240                   | VVIVI 1000                |                   | 1200                   |                 |                  |                     |                     |                     |                  | 0                    |

- When conversion control "EN" = 1 or "EN↑" (☐ instruction) has a transition from 0 to 1, will convert alphabets and numbers stored in S (S has a maximum of 12 alphanumeric character) into ASCII and store it into registers starting from D. Each 2 alphanumeric characters occupy one 16-bit register.

- The application of this instruction, most often, stores alphanumeric information within a program, and waits until certain conditions occur, then converts this alphanumeric information into ASCII and conveys it to external display devices which can accept ASCII code.

$$X0$$

$EN^{\uparrow}$

$S: ABCDEF$

$D: R 0$

The instruction at left converts the 6 alphabets -ABCDEF into ASCII then stores it into 3 successive registers starting from R0.

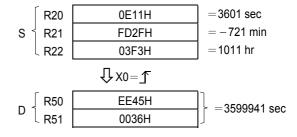

FUN 61 ₽ →SEC

#### Hour:Minute:Second to Seconds Conversion

FUN 61

→SEC

Conversion control  $-EN^{\uparrow}$   $\begin{array}{c}

61P. \rightarrow SEC \\

S : \\

D :

\end{array}$  -D=0 - Result as 0

- S : Starting calendar data register to be converted

- D: Starting register storing results

| Range | WX    | WY    | WM     | WS    | TMR  | CTR  | HR    | IR    | OR    | SR    | ROR   | DR    | K          |

|-------|-------|-------|--------|-------|------|------|-------|-------|-------|-------|-------|-------|------------|

|       | WX0   | WY0   | WM0    | WS0   | T0   | C0   | R0    | R3840 | R3904 | R3968 | R5000 | D0    | -117968399 |

| Ope-  |       |       |        |       |      |      |       |       |       |       |       |       |            |

| rand  | WX240 | WY240 | WM1896 | WS984 | T255 | C255 | R3839 | R3903 | R3967 | R4167 | R8071 | D3071 | 117964799  |

| S     | 0     | 0     | 0      | 0     | 0    | 0    | 0     | 0     | 0     | 0     | 0     | 0     | 0          |

| D     |       | 0     | 0      | 0     | 0    |      | 0     |       | 0     | O*    | O*    | 0     |            |

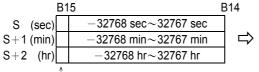

- When conversion control "EN" = 1 or "EN↑" (☐ instruction) has a transition from 0 to 1, will convert the hour: minute: second data of S~S+2 into an equivalent value in seconds and store it into the 32-bit register formed by combining D and D+1. If the result = 0, then set the "D = 0" flag as 1.

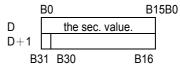

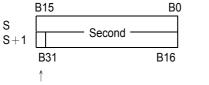

- Among the FB-PLC instructions, the hour: minute: second time related instructions (FUN61 and 62) use 3 words of register to store the time data, as shown in the diagram below. The first word is the second register, the second word is the minute register, and finally the third word is the hour register, and in the 16 bits of each register, only B14~B0 are used to represent the time value. While bit B15 is used to express whether the time values are positive or negative. When B15 is 0, it represents a positive time value, and when B15 is 1 it represents a negative time value. The B14~B0 time value is represented in binary, and when the time value is negative, B14~B0 is represented with the 2's complement. The number of seconds that results from this operation is the result of summation of seconds from the three registers representing hours: minutes: seconds.

The B15 of each registers is used to represent the sign of each time value

B31 is used to represent the positive or negative nature of the sec. value

- Besides FUN61 or 62 instruction which treat hour: minute: second registers as an integral data, other instructions treat it as individual registers.

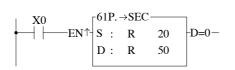

- The example program at below converts the hour: minute: second data formed by R20~R22 into their equivalent value in seconds then stored in the 32-bit register formed by R50~R51. The results are shown below.

FUN 62

→ HMS

SECOND→HOUR : MINUTE : SECOND

→ HMS

- S :Starting register of second to be converted

- D :Starting register storing result of conversion (hour : minute : second)

| Range | WX    | WY    | WM      | WS    | TMR  | CTR  | HR    | IR    | OR    | SR    | ROR   | DR    | K          |

|-------|-------|-------|---------|-------|------|------|-------|-------|-------|-------|-------|-------|------------|

|       | WX0   | WY0   | WM0     | WS0   | T0   | C0   | R0    | R3840 | R3904 | R3968 | R5000 | D0    | -117968399 |

| Ope-  |       |       |         |       |      |      |       |       |       |       |       |       |            |

| rand  | WX240 | WY240 | WM1896  | WS984 | T255 | C255 | R3839 | R3903 | R3967 | R4167 | R8071 | D3071 | 117964799  |

| S     | 0     | 0     | $\circ$ | 0     | 0    | 0    | 0     | 0     | 0     | 0     | 0     | 0     | 0          |

| D     |       | 0     | 0       | 0     | 0    | 0    | 0     |       | 0     | O*    | O*    | 0     |            |

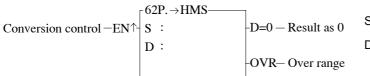

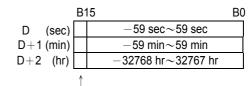

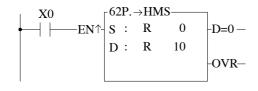

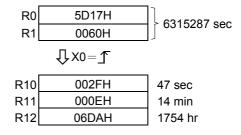

• When conversion control "EN" = 1 or "EN↑" (☐ instruction) has a transition from 0 to 1, will convert the second data from the S~S+1 32-bit register into the equivalent hour: minute: second time value and store it in the three successive registers D~D+2. All the data in this instruction is represented in binary (if there is a negative value it is represented using the 2's complement.)

The bit B31 of the second register is used as the sign bit of the second value.

The bits B15 of each register are used as the sign bit of the hour : minute : second value

- As shown in the diagram above, after convert to hour: minute: second value, the minute: second value can only be in the range of -59 to 59, and the hour number can be in the range of -32768 to 32767 hours. Because of this, the maximum limit of D is -32768 hours, -59 minutes, -59 seconds to 32767 hours, 59 minutes, 59 seconds, the corresponding second value of S which is in the range of -117968399 to 117964799 seconds. If the S value exceeds this range, this instruction cannot be carried out, and will set the over range flag "OVR" to 1. If S = 0 then result is 0 flag "D = 0" will be set to 1.

- The program in the diagram below is an example of this instruction. Please note that the content of the registers are denoted by hexadecimal, and on the right is its equivalent value in decimal notation.

FUN 63 ₽ →HEX

#### Conversion of ASCII code to hexadecimal value

FUN 63 ₽ →HEX

Conversion control  $-EN^{\uparrow}$   $S : \\ N : \\ D :$  -ERR -

S: Starting source register.

N : Number of ASCII codes to be converted to hexadecimal values.

D: The starting register that stores the result (hexadecimal value).

S, N, D, can associate with V, Z to do the indirect addressing application.

| Range        | WX    | WY    | WM     | WS    | TMR  | CTR  | HR    | IR    | OR    | SR    | ROR   | DR    | K       | XR      |

|--------------|-------|-------|--------|-------|------|------|-------|-------|-------|-------|-------|-------|---------|---------|

| One-         | WX0   | WY0   | WM0    | WS0   | T0   | C0   | R0    | R3840 | R3904 | R3968 | R5000 | D0    | 16-bit  | V       |

| Ope-<br>rand | WX240 | WY240 | WM1896 | WS984 | T255 | C255 | R3839 | R3903 | R3967 | R4167 | R8071 | D3071 | +number | Z       |

| S            | 0     | 0     | 0      | 0     | 0    | 0    | 0     | 0     | 0     | 0     | 0     | 0     |         | $\circ$ |

| N            | 0     | 0     | 0      | 0     | 0    | 0    | 0     | 0     | 0     | 0     | 0     | 0     | 1~511   | $\circ$ |

| D            |       | 0     | 0      | 0     | 0    | 0    | 0     |       | 0     | O*    | O*    | 0     |         | $\circ$ |

- When conversion control "EN" =1 or "EN↑" (☐ instruction) changes from 0→1, it will convert the N successive hexadecimal ASCII character('0'~'9','A'~'F') convey by 16 bit registers (Low Byte is effective) into hexadecimal value, and store the result into the register starting with D. Every 4 ASCII code is stored in one register. The nibbles of register, which does not involve in the conversion of ASCII code will remain unchanged.

- The conversion will not be performed when N is 0 or greater than 511.

- $\bullet$  When there is ASCII error (neither 30H $\sim$ 39H nor 41H $\sim$ 46H), the output "ERR" is ON.

- The main purpose of this instruction is to convert the hexadecimal ASCII character ('0'~'9','A'~'F'), which is received by communication port1 or communication port2 from the external ASCII peripherals, to the hexadecimal values that the CPU can process directly.

#### Code conversion instructions

### FUN 63 P $\rightarrow$ HEX

#### Conversion of ASCII code to hexadecimal value

FUN 63 P  $\rightarrow$ HEX

⟨ Example 1 ⟩ When M1 from OFF→ON, ASCII code converted to hexadecimal value.

Originally R100=0000H R0=0039H (9) **→** R100=0009H

〈Example 2〉 When M1 is ON, ASCII code converted to hexadecimal value.

remain unchanged) of R100

$R0\!=\!0039H\;(\,9\,)\qquad \quad \text{Originally R100}\!=\!0000H$ R1=0041H (A) → R100=009AH

〈Example 3〉 When M1 is ON, ASCII code converted to hexadecimal value.

R0=0039H (9) Originally R100=0000H R1=0041H (A) R2=0045H (E) **→** R100=09AEH

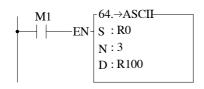

$\langle$  Example 4  $\rangle$  When M1 is ON, ASCII code converted to hexadecimal value.

Converts the ASCII code of R0~R5 into hexadecimal value and store it to R100~P104

Originally R100=0000H R0=0031H(1) R1=0032H(2) R101=0000H R2=0033H(3) R3=0034H (4) R4=0035H (5) → R100=3456H R5=0036H (6) R101=0012H

| FUN             | 64 | P |

|-----------------|----|---|

| $\rightarrow$ A | SC | Ш |

# Conversion of hexadecimal value to ASCII code

FUN 64 ₽ →ASCII

Conversion control—EN $\uparrow$ -S : N : D :

S : Starting source register

N : Number of hexadecimal digit to be converted to ASCII code.

D: The starting register storing result.

S, N, D, can associate with V, Z to do the indirect addressing application.

| Range | WX    | WY    | WM     | WS    | TMR  | CTR  | HR    | IR    | OR    | SR    | ROR   | DR    | K        | XR      |

|-------|-------|-------|--------|-------|------|------|-------|-------|-------|-------|-------|-------|----------|---------|

| Ope-  | WX0   | WY0   | WM0    | WS0   | T0   | C0   | R0    | R3840 | R3904 | R3968 | R5000 | D0    | 16-bit   | ٧ .     |

| rand  | WX240 | WY240 | WM1896 | WS984 | T255 | C255 | R3839 | R3903 | R3967 | R4167 | R8071 | D3071 | + number | Z       |

| S     | 0     | 0     | 0      | 0     | 0    | 0    | 0     | 0     | 0     | 0     | 0     | 0     |          | $\circ$ |

| N     | 0     | 0     | 0      | 0     | 0    | 0    | 0     | 0     | 0     | 0     | 0     | 0     | 1~511    | $\circ$ |

| D     |       | 0     | 0      | 0     | 0    | 0    | 0     |       | 0     | O*    | O*    | 0     |          | $\circ$ |

- When conversion control "EN" =1 or "EN↑" (☐ instruction) changes from 0→1, will convert the N successive nibbles of hexadecimal value in registers start from S into ASCII code, and store the result to low byte (high byte remain unchanged) of the registers which start from D.

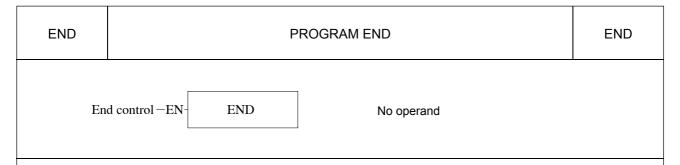

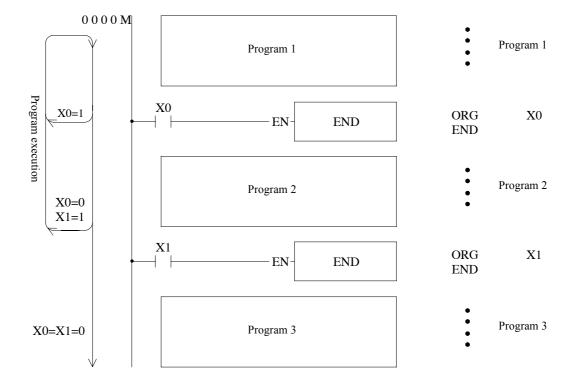

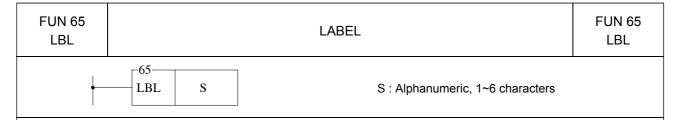

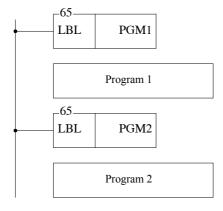

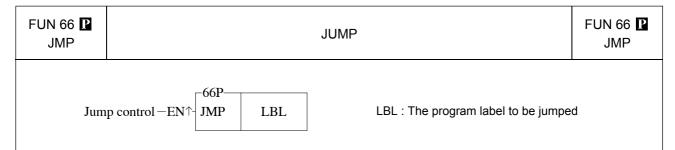

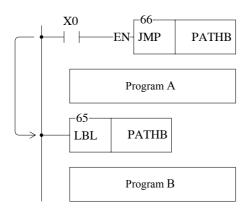

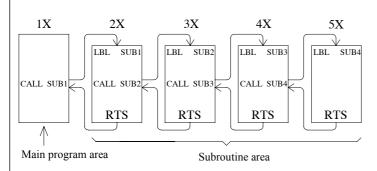

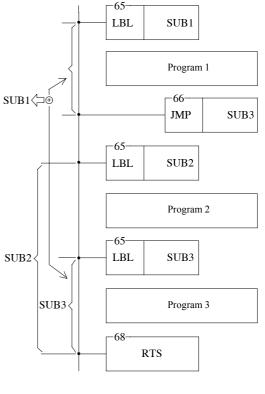

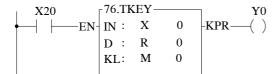

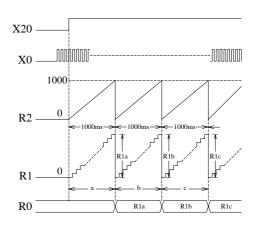

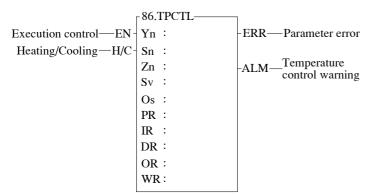

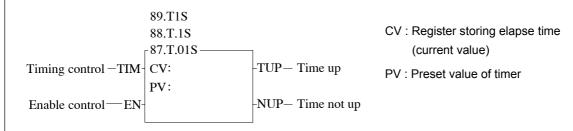

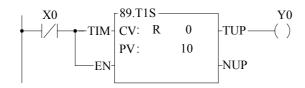

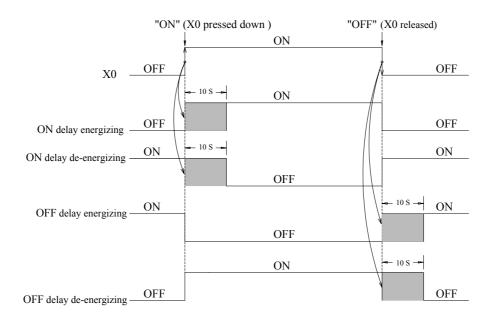

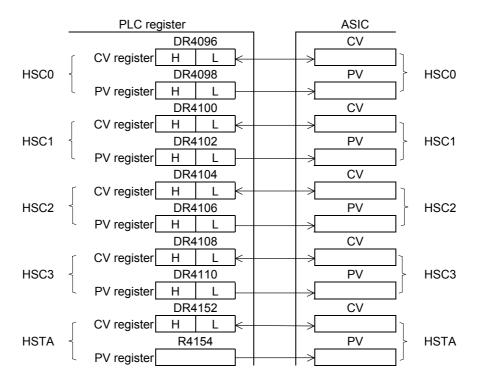

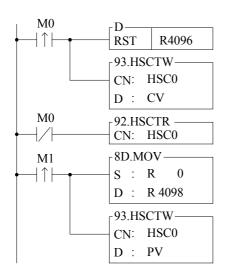

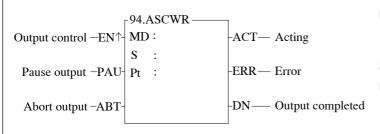

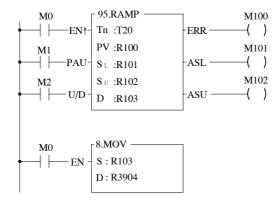

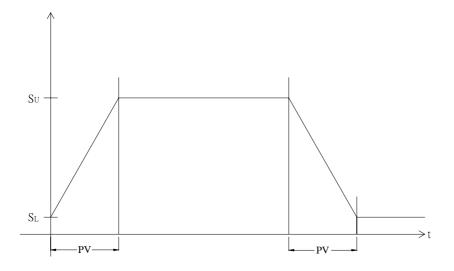

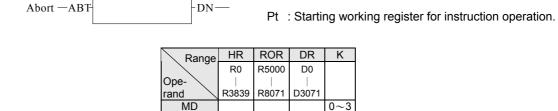

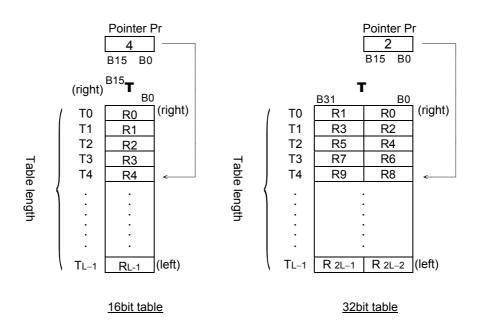

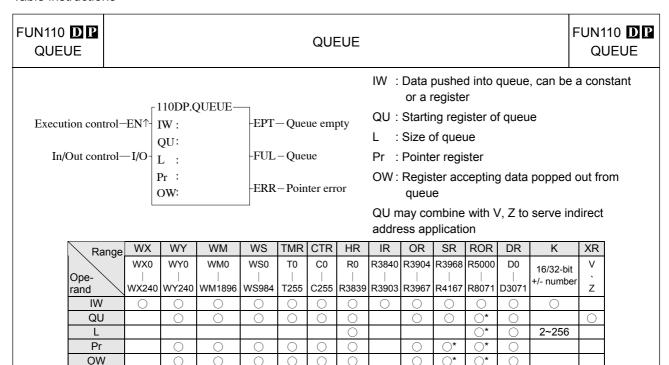

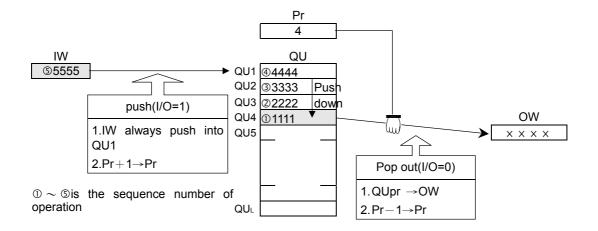

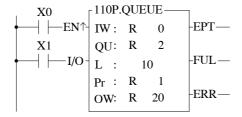

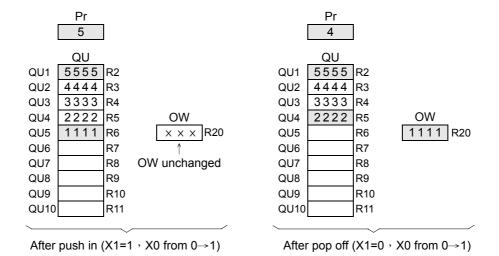

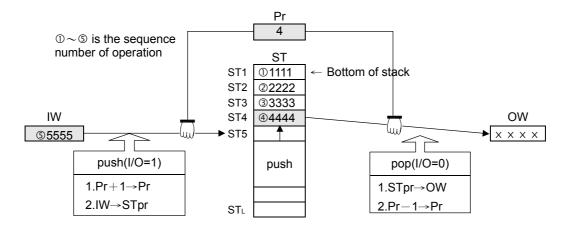

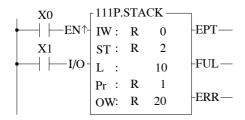

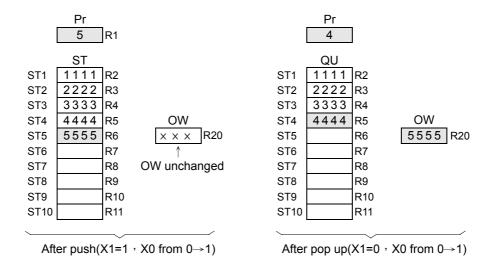

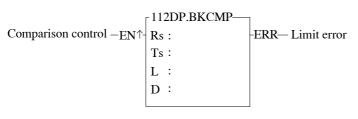

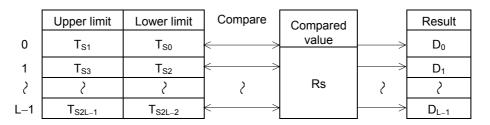

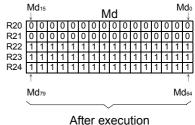

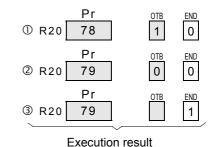

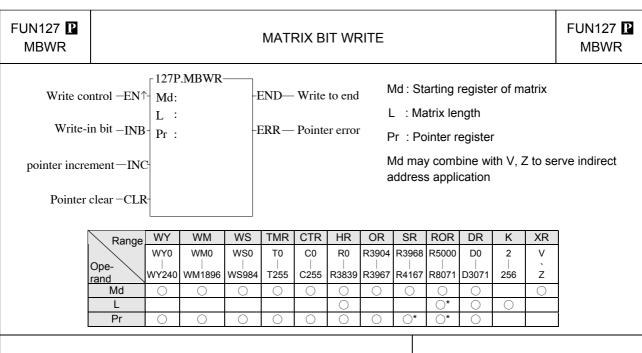

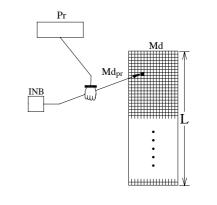

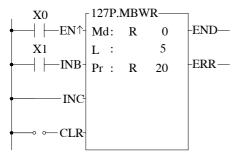

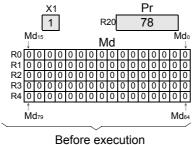

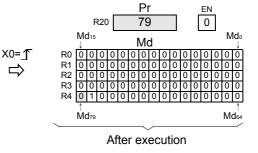

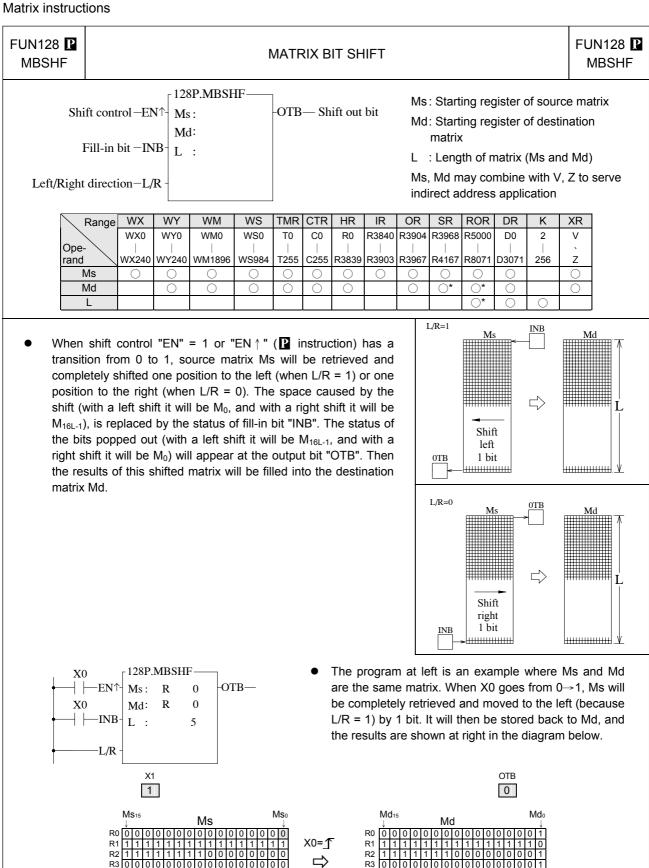

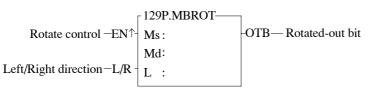

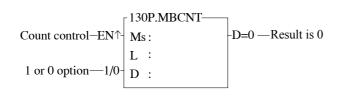

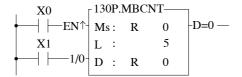

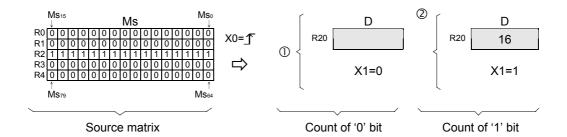

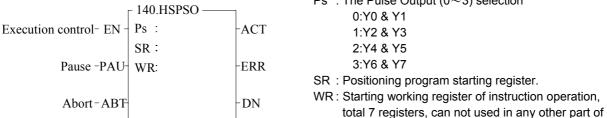

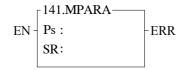

- The conversion will not be performed when the value of N is 0 or greater than 511.